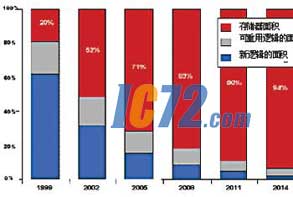

图1 SoC中各种逻辑的比重

另一方面,微处理器的速度以每年60%递增,但主存的速度每年仅增长10%左右。二者之间的性能差异越来越大。计算机设计者们面临了“存储器障碍(Memory Wall)”问题,存储器带宽成为限制系统性能最严重的瓶颈之一。这一瓶颈也迫使人们将越来越大的存储器与处理器集成在一起,利用片上总线的带宽优势,以更高的速度向处理器提供数据。

其实嵌入式存储器早已不是新鲜事物,实际上,通用微处理器中的寄存器、一级Cache、二级Cache都是“嵌入”在芯片中的高速存储器。大容量的 Cache对于提升CPU性能的作用非常明显。Intel先进的Itanium 2处理器已经集成了3MB的三级Cache。嵌入式存储器的优势已经开始被IC设计者们所青睐。

嵌入式存储的优势

更高的带宽

将存储器集成在片上之后,我们可以在片内设计非常宽的总线,不再采用I/O引脚和带宽受限的片外总线。并且由于避免了驱动大的I/O电容,片内的频率将大大提高。这样,嵌入式存储器就能够为其他片上逻辑提供更高的数据带宽。例如,如果设计256位的嵌入式DRAM总线,使其工作在500MHz频率下,那么其峰值带宽就可以达到128Gb/s,这是目前最先进的DDR存储器都望尘莫及的。

更低的系统功耗

片外互连需要很大的I/O驱动,以克服封装和PCB布线的电容与阻抗,从而限制了片外存储系统的工作速度。另外,驱动大型的I/O缓冲所产生的巨大功耗,对于采用电池供电的便携式应用是非常不利的。而嵌入式存储器避免了大的I/O驱动,同时可以采用降频、降压、待机等灵活的低功耗设计方法,有效降低系统功耗。例如,采用嵌入式DRAM的单片图形控制器的平均功耗在500~750mW,相比多芯片方案的2.5W降低了75%的功耗。

更优化的粒度和存储结构

通过专门的定制设计和结构优化,嵌入式存储器可以很好的解决存储粒度的问题。例如,图像帧缓冲器的大小取决于所需的分辨率、色彩深度、3D渲染能力等因素。而单颗存储器的密度往往跨越较大,用户能够购买的容量一般都大大超过了实际需要的容量,造成了不必要的成本浪费和功耗。片上存储器的密度是可以灵活定制的,设计者可以根据用户的需要设置存储阵列的形状、朝向和位置,或者采用多个子阵列,从而实现与其余逻辑更简化、高速的互连,优化了整个系统的结构。

更高的可靠性和更紧凑的系统结构

通过将多个芯片集成在一起,减少了元件个数,节省了PCB面积,我们能够采用更小、更紧凑的系统实现给定的功能。这对于移动计算、通信产品、智能卡、汽车电子等嵌入式应用来说都是非常必要的。另外,将存储器和逻辑集成在一块芯片上降低了多片分别封装的成本,提高了系统的可靠性和电磁兼容性。

更好的工艺缩放特性

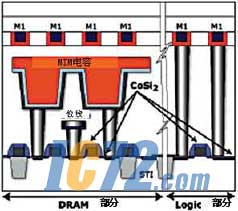

随着工艺的进步和电路设计水平的提高,人们逐步实现了嵌入式存储器与常规CMOS逻辑工艺的兼容,从而使嵌入式存储器也能够按比例缩减单元尺寸,提供更快的访问速度和更高的存储密度。NEC就克服了低温电容的难题,推出了的180nm工艺下MIS结构的嵌入式DRAM和150nm工艺下MIM结构的全金属嵌入式DRAM,并实现了与CMOS逻辑工艺的兼容,如图2所示。

图2 NEC的MIM结构的嵌入式DRAM剖面

嵌入式存储面临的挑战

工艺

逻辑工艺和存储器工艺从本质上来说是不同的,某些地方甚至是矛盾的。首先,二者的互连需求不同。存储器非常规整,常成块出现,所需的互连比较少。而逻辑模块常常散列在芯片各个地方,对互连的要求很高。其次,二者的金属工艺层次不同。逻辑工艺共4~6层,其中只有1~2层多晶,其余为金属层。而存储器工艺常常需要4层以上的多晶。每增加一层金属或者多晶都会增大成本、复杂性和制造时间。

逻辑设计中要使用较宽的金属线中心距,以减小阻抗和布线延迟,而DRAM设计中为了保证紧凑的阵列结构,常使用较窄较慢的金属线。标准逻辑的工艺常采用较薄的栅氧层,以降低开启电压,减少开关时间,实现高速操作。而存储器工艺常使用较厚的栅氧层,以减少漏电流,减少刷新操作(DRAM必须的),从而降低功耗,同时还能够改善数据保持特性,增强cell对编程高电压、电场的抵御能力。另外,Flash等存储器需要高电压编程,相应需要大量的隔离电路,从而增大了制造复杂性和芯片设计难度。

随着逻辑工艺尺寸的不断缩减,需要制作电容的嵌入式DRAM、FeRAM、MRAM等存储器面临难以同步缩小的难题,因为缩小的电容无法存储足够的电荷,可靠性大大降低。

因此,限制嵌入式存储器发展的最大障碍就是与CMOS逻辑工艺的兼容问题,虽然有所突破,但是距离成熟的普及应用还有很长的路要走。

成品率

嵌入式存储器面临的成品率问题来源于两个方面:首先,嵌入式存储器的设计规则比常规CMOS逻辑规则更加大胆,容易带来制造缺陷和可靠性问题。另外,正如图1所示,存储器在SoC中所占的比重越来越高,因此SoC的总成品率在很大程度上取决于存储器的成品率。

通过设置冗余存储单元的方式可以提高成品率,但是如何检测和定位存储器中的缺陷,如何分配冗余单元,都需要涉及缺陷分布的工艺制造知识,需要相应工艺下存储器设计的经验和历史统计信息,才能决定合适的冗余单元类型和数量。过多的冗余单元意味着不必要的芯片面积和制造成本。

另外,在设计存储器IP模块(宏单元)的时候,就对其进行工艺验证和成品率优化,从而在集成到SoC中之前完成优化工作,可以缩短SoC的迭代周期和量产时间。

测试与修复

为了提高成品率,减小测试开销,新一代的嵌入式存储器通常拥有内建的扫描锁存器和扫描路径,以及BIST(Built-In-Self-Test,内建自测)逻辑和BISR(Built-In-Self-Repair)电路。这些诊断电路能够确定缺陷存储单元的位置,并采用地址映射逻辑自动映射到冗余的地址空间。BISR方法增加了地址的建立时间,而且必须与其他CMOS逻辑有机结合,才能形成高效的测试引擎,否则反而会成为高速逻辑的负担。

嵌入式易失性存储器

eSRAM

嵌入式SRAM(eSRAM)是最早、最成熟的嵌入式存储器,广泛应用在通用CPU的片内高速缓存、网络处理器中的帧缓冲器等领域。嵌入式SRAM 基于标准的CMOS逻辑工艺,在制作时不需要增加额外的工艺步骤。传统的eSRAM都是六管结构,单元尺寸较大,难以实现大规模的集成。因此,人们相继研制出了单管(1T)和四管(4T)eSRAM结构。

Mosys公司提出的1T SRAM单元包括一个电容和一个访问管,与平面DRAM单元非常相似,只是用一个MOS结构代替了DRAM的电容。这种单元的面积只有传统SRAM单元的 1/3到1/4,并且容易按比例缩小。但是这种MOS电容能够存储的电荷比较少,需要专门的线性偏置电路来进行补偿,软误差率(SER)也较高。

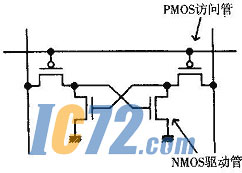

无负载四管CMOS SRAM单元的尺寸只有传统六管单元的56%,能够提高存储容量和工作速度。但是这种存储单元要求能够产生精确的时序信号,保证在不同的温度条件下静态数据的保持特性,并且要克服单元电流小、位线耦合电容大等不利影响。图3给出了4T SRAM的结构。

图3 4T无负载SRAM单元

随着微电子工艺的发展,eSRAM面临的最大问题就是漏电流的问题。eSRAM的漏流包括亚阈漏流、GIDL(Gate Induced Drain Leakage和栅极隧穿电流。在90nm工艺下,亚阈漏流和GIDL就开始明显增大,在65nm工艺下,栅极的隧穿漏流也将变大。为了减少漏流,一种办法就是在SRAM单元中使用相对较高的阈值电压Vth。另外为了保持性能,在SRAM单元中使用较高的电源电压Vdd,这样也有利于SRAM单元保持较高的静态噪声容限(static noise margin,SNM)。但是高Vdd使芯片设计更加复杂,还要解决eSRAM和逻辑之间电源线的隔离与布线问题。还有一些电路设计技术研究如何在待机模式下抬高阈值电压Vth,在工作模式下降低Vth。

eDRAM

某些SoC应用需要高密度和高带宽的嵌入式存储器。嵌入式DRAM(eDRAM)的特性恰好能够满足这一要求。eDRAM的宏单元面积仅仅是eSRAM宏单元面积的1/3到1/4,相比之下,更容易实现大规模的集成。

eDRAM中的敏感放大器可以作为临时数据锁存器,存储器宏单元和周围逻辑电路之间可以设置非常宽的数据总线,从而实现极高的存储带宽。eDRAM的并行大块数据传输能力非常适合数据流为主的应用,例如图形或网络芯片。

eDRAM工艺的核心是用于存储电荷的电容的结构。目前两种主要的电容结构是层叠式(stacked)电容和沟槽式(trench)电容。两种结构的电容各有千秋:

沟槽电容在衬底中制作电容,在给定的面积上能够实现更密集的电容,单元尺寸较小,所需的多晶硅层数少,不需要复杂的多晶平整工艺,也不会由于淀积多晶而影响已有的晶体管结构;但是沟槽电容需要高精度,对于0.18μm以后的工艺,制造非常困难;层叠电容由多层多晶构成电容,存储电荷量较大,但是其所需掩模层数较多,需要复杂的平整工艺。

IBM、西门子和东芝是沟槽式DRAM电容的拥护者;三菱和三星则是层叠式DRAM电容的拥护者。IBM在0.11μm工艺下为ASIC芯片CU-11开发的第三代嵌入式DRAM核,密度为SRAM的4倍,采用GND预充技术。

NEC 采用MIM(金属-绝缘层-金属)结构的电容制作eDRAM的存储单元。这种结构的电容与传统PIP(多晶-绝缘层-多晶)结构的电容相比具有更低工艺温度,从而有效减少了制造过程中影响晶体管性能的热处理过程,实现了与标准CMOS工艺的完全兼容。在130nm工艺下,NEC推出的eDRAM能够在 1.2V电压下达到314MHz的随机访问频率。在90nm工艺下,NEC采用二氧化锆(ZrO2)作为电介质材料,大大提高了介电常数,降低了漏电流和工艺温度。

嵌入式非易失性存储器

很多应用都需要在掉电后仍然能够保持数据的存储器,例如智能卡。非易失性存储器保持数据的特性是eSRAM和eDRAM所无法比拟的。

eFlash

嵌入式系统设计师们都喜欢使用基于Flash的处理器。因为在产品开发和生产的早期阶段,片上Flash的灵活性大大提高了软件开发的速度,并且允许在最后一分钟修改软件。在整个产品周期中,嵌入式Flash对于系统维护、软件在线更新都是非常方便的,设计师不需要更换新的器件。嵌入式Flash和微控制器组合在一起,广泛应用于手机、笔记本电脑、掌上电脑、数码相机等领域。可以说,几乎在每个人的生活中都能够找到嵌入式Flash的影子。

TSMC于2005年推出了0.18μm的eFlash工艺,该工艺不需要增加额外的掩模,适合小存储密度的芯片识别领域、中等密度MCU的应用。

Motorola公司的16位微控制器68HC12内嵌了4KB的Flash存储器。Hitachi公司研制的32位RISC微控制器SH7047F和TI公司的32位微控制器TMS470都集成了高达256KB的Flash。

目前,一种新型的嵌入式Flash存储器结构称为Micro-flash,它能够与标准CMOS工艺兼容,通常用于SoC等方面的应用。Micro -flash工艺使用了不挥发只读存储器(NROM)技术,存储单元是一个n沟道MOS管,它的绝缘层采用了两层二氧化硅夹一层捕获材料的三明治结构,称为ONO(氧化物-氮化物-氧化物)结构。Micro-flash单元相比传统的Flash单元面积小4~6倍。经过高温存储寿命(HTSL)测试, Micro-flash器件显示了与浮栅器件相当的数据保持特性,擦写周期测试则显示它具有105次以上的循环擦写能力。

FeRAM

铁电存储器(FeRAM)是一种采用铁电效应作为电荷存储机制的、基于RAM的器件。铁电效应是材料在没有外加电场的情况下存储电极化状态的能力。 FeRAM的存储单元是通过在两个电极板之间积淀一层铁电晶体薄膜以形成一个电容而制作的。这个电容与DRAM的电容非常相似,但是与DRAM将数据用电荷的形式存储在电容中不同,FeRAM将数据存储在一个晶体结构中。铁电材料的晶体结构中保持着两个稳定的、由内部偶极子的排列产生的极化状态,分别表示 “1”和“0”。

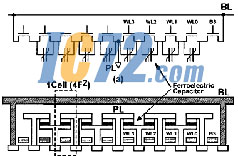

已实现的商用分立型FeRAM产品容量为512Kb,单元大小为6μm2。东芝最近开发的FeRAM技术实现了0.6μm2的存储单元尺寸,结合 “链式FeRAM” 结构,能够实现大容量高密度的非易失性存储器宏单元。新型的“单掩模蚀刻”工艺技术使连续刻蚀工艺成为可能,从而大大减小了存储单元面积,生产出32Mb 的样片。图4给出了“链式FeRAM”的电路结构和截面图。

图4 链式FeRAM两个单元的电路图

FeRAM制造工艺可以与标准的CMOS工艺直接兼容。在完成标准CMOS底层工艺后,就制造铁电电容,然后进行互连和钝化工艺。但是,FeRAM 工艺确实需要一些在常规半导体工艺中不采用的材料,如作为电容电极的Pt和铁电材料本身。此外,FeRAM的耐久性有限,因为铁电效应需要一个原子的移动。FeRAM的读出是破坏性的,读出耐久性受到写耐久性的限制。

MRAM

磁阻存储器(MRAM)的出现为嵌入式存储器指出了一条统一大道,因为这种存储器集SRAM的高速度、DRAM的高密度、Flash的非易失性、擦写耐久性为一体,同时能够工作在极低的电压下,具有很小的功耗,是一种“全功能”的固态存储器,应用前景十分诱人。

MRAM是利用材料的磁阻随磁场的作用而改变的原理制成的。它的磁存储单元由三层结构的磁薄膜构成,薄膜之间用绝缘层分开,避免交叉耦合。MRAM 存储的数据是由上下两层薄膜的磁化方向决定的,由电阻测量实现数据读出。如果磁化方向是平行的,就会导致较低的电阻,存储数据“0”;如果磁化方向相反,就会导致较高的电阻,存储数据“1”。写入时,利用写入电流产生的磁场改变磁薄膜的磁化方向。MRAM在写入时需要较大的写电流,这一点对减小单元大小、隔离外围电路和降低低功耗都产生了不利影响。

MRAM在制作时只需要增加3~4层掩模板,就可以把嵌入式MRAM做到CMOS逻辑中去。相比之下,eFlash和eDRAM都需要增加更多的额外工艺步骤。

MRAM技术得到了人们广泛的关注和支持。美国国防部高级研究项目机构(DARPA)早在1994年就投资研究MRAM。飞思卡尔、飞利浦和英飞凌公司都开展了MRAM的研究。目前,飞思卡尔已经推出了4Mb的MRAM样片。这种样片采用0.18μm工艺制造,访问时间为25ns或者35ns。东芝和瑞萨半导体自从2002年以来一直在合作开发MRAM技术,他们计划在今年年底推出256Mb的MRAM样片。2006年,消费者将在市场上看到第一批 MRAM器件。如果一切顺利,在2007年,MRAM将实现更高的密度,将在蜂窝电话等应用领域与Flash展开激烈竞争。

PCRAM

相变非易失性存储器(PCRAM)技术利用某些薄膜合金的结构相变存储信息。这些合金具有两种稳定的状态:(a)多晶状态,具有高反射和低电阻的性质;(b)无定形状态,是无光泽和高电阻的。采用能够转换两个状态的电脉冲就可以控制两个状态快速地翻转和变相。常用的相变合金是VI族(硫族)化合物材料,例如锗、锑和碲。

PCRAM成功的关键在于合金薄膜的品质。PCRAM的擦写耐久时间小于1012次,这会限制其应用,但是新的材料或工艺会解决这一问题。

Ovonyx公司与Intel公司和BAE Systems公司合作,积极研发PCRAM技术,已经研发出了256Kb的存储单元阵列样片,并计划进一步推出256Mb和更高密度的芯片。

嵌入式存储的未来

嵌入式存储器具有先进的存储概念和大容量集成的优势,是SoC的重要组成部分,具有重要的创新性和实用性。嵌入式存储器能否取得最终的成功,取决于多方面的因素:

能否与标准CMOS工艺兼容,在不增加复杂的工艺步骤的基础上,实现大容量的片上集成,从而提高其性价比;能否随着工艺的发展按比例缩小,解决超深亚微米工艺的延续性和扩展性问题,这是所有采用电容结构存储信息的存储器共同面临的挑战;能否满足片上其他高速逻辑的带宽需要,构成带宽均衡、稳定简洁的集成系统;准确的市场定位,保持量产。

为此,系统结构师、电路设计师和制造工艺师必须共同努力,密切跟踪市场的需要,从新的电路结构、新工艺、新材料三个方面共同解决工艺缩小后面临的诸多挑战,不断推出技术先进、功能强大的基于嵌入式存储器的系统。

此外,还有一些新型的存储器,例如质子非易失性存储器、基于晶闸管的SRAM单元、纳米存储器、固态全息存储器等,如果这些存储器突破了工艺集成的障碍,也将会成为嵌入式存储器市场的有力竞争者。