进入21世纪后,人类社会已全面进入信息时代,信息产业成为了现代社会最重要的支柱和最主要的产业,伴随着半导体技术、数字信号处理技术及通信技术的飞速发展,A/D、D/A转换器近年也呈现高速发展趋势,而随着高速、高精度A/D转换器(ADC)的发展,尤其是能直接进行中频采样的高分辨率数据转换器的上市,对稳定的采样时钟的需求越来越迫切,随着通信系统中的时钟速度迈入GHz级,相位噪声和时钟抖动已成为模拟设计中必须要考虑的因素。

数据转换器的主要作用要么是由定期的时间采样产生模拟波形,要么是由一个模拟信号产生一系列定期的时间采样。因此,采样时钟的稳定性十分重要,从数据转换器的角度来看,这种不稳定性(亦即随机的时钟抖动),会在模数转换器何时对输入信号进行采样方面产生不确定性,在高速系统中,时钟或振荡器波形的时序误差会限制一个数字I/O接口的最大速率,不仅如此,它还会增大通信链路的误码率,甚至限制A/D转换器(ADC)的动态范围,数据转换器要想获得最佳性能,恰当地选择采样编码时钟是极为重要的。

ADC电路

近年来,国外对高速A/D转换器的研究最为活跃,并在基本的Flash结构上出现了一些改进结构[2],如分区式分级(Subranging)电路结构(如half-flash结构、Pipelined、Multistage结构、Multistep结构)。实际上,他们是由多个Flash电路结构与其他功能电路采用不同形式的组合而成的电路结构,这种结构可弥补基本Flash电路结构的缺陷,是实现高速、高分辨率A/D转换器的优良电路设计技术,这种结构在逐步取代历史悠久的SAR和积分型结构,另外还有一类每级一位(bit-per-stage)电路结构,在它的基础上进一步改进,就得到一种称为Folding(折叠式)的电路结构(又称为Mag Amps结构)这是一种Gray码串行输出结构,这些电路设计技术为高速、高分辨率,高性能A/D转换器的发展起到了积极的推动作用。

另外,在高分辨率A/D转换器电路设计技术中,Σ-Δ电路结构是目前很流行的一种电路设计技术,这种电路结构不仅在高分辨低速或中速A/D转换器方面将逐步取代SAR和积分型电路结构,而且这种结构同流水线结构相结合,有望实现更高分辨率、和更高速的A/D转换器。

时钟占空比稳定电路

随着新时期武器装备中电子系统功能的不断扩大及性能的不断提高,电子系统的复杂程度也不断增加,为了保证电子系统的数据采样、控制反馈和数字处理的能力和性能,现代军用电子系统对A/D转换器的要求也越来越高,尤其是军事数据通讯系统,数据采集系统,对高速、高分辨率A/D转换器的需求在不断增加,时钟占空比稳定电路作为高速、高精度A/D转换器的核心单元,对转换器的信噪比(SNR)和有效位(ENOB)等性能起至关重要的作用,因此要保证高速、高精度A/D转换器的性能,必须首先保证采样编码时钟具有合适的占空比和很小的抖动,因此,开展时钟占空比稳定电路的研究十分需要。

由于时钟占空比稳定电路是高速、高精度A/D转换器的核心单元,而单独的时钟占空比稳定电路产品几乎没有,只有在高速、高精度A/D转换器中才有报道,ADI公司产品与其他公司产品相比之所以能提高采样性能,主要得益于对DCS(duty cycle stabilizer)电路的改进,DCS电路负担着减小时钟信号抖动的作用,而采样时序就取决于时钟信号,各家公司过去的DCS电路只能将抖动控制在0.25ps左右,而高性能新产品AD9446和LTC2208则可将抖动降低到50fs左右,通常降低抖动就能够改善SNR,从而提高有效分辨率(ENOB:有效比特数),并在达到16比特量子化位数的同时,能实现100Msps以上的采样速率,如果不控制抖动就提高采样速率,则会降低ENOB,且无法获得希望的分辨率,也无法提高量子化位数,DCS电路随着高性能A/D转换器的发展,可向更高速度,更小抖动和稳定方向发展,表1所列为国外A/D转换器中时钟占空比稳定电路的主要技术和参数指标。

事实上,至今为止,AD公司的60fs的抖动已经是最小的了,现在孔径抖动一般控制在1个ps左右,高于这个数甚至高达几十个ps的抖动实际上已经没有多大的意义了。

时钟稳定电路的实现方法

从目前国内外研究的情况看,用于稳定高速ADC的时钟电路主要是锁相环路(Phase-locked loop,PLL)。锁相系统在本质上讲是一个闭环相位控制系统,简单得讲,它是一种能使输出信号在频率和相位上与输入信号同步的电路,即系统进入锁定状态(或同步状态)后,振荡器输出信号与输入信号之间的相差为零或保持常数,由于锁相环路具有许多优良特性,故可广泛用于高性能处理器的时钟产生以及分布、系统的频率合成与变换、自动频率调谐跟踪、数字通信中的位同步提取、锁相、锁相倍频与分频等。

本文提出了一种延迟锁相环(Delay -locked loop DLL)的设计方案,事实上,PLL主要是利用其中的鉴相器和滤波器监测反馈时钟信号与输入时钟信号,然后用产生的电压差控制压控振荡器,从而产生一个近似于输入时钟的信号,最终达到锁频之目的,DLL的作用就是在输入时钟和反馈时钟之间插入延时脉冲,直到这两个时钟上升沿对齐,并达到同步,当输入时钟脉冲沿和反馈脉冲沿对齐后,片上延时锁相环DLL才能都被锁定。锁定时钟后,电路不再调整,两个时钟也没有什么差别,这样,片上延时锁相环就用DLL输出时钟补偿了时钟分配网络造成的时间延迟,从而有效地改善了时钟源和负载之间的时间延迟。首先,延迟线与振荡器相比,受噪声较小,这是因为波形中被损坏的过零点在延迟线的末端就消失了,而在振荡器电路中又会再循环,因而会产生更多的损坏,其次,DLL中控制电压的变化内迅速改变延迟时间,也就是说,传输函数简单地等于VCDL的增益KBCDL,总之,PLL中用到的振荡器存在着不稳定性和相位偏移的积累,因而在补偿时钟分别在网络造成时间延迟时,往往会降低PLL的性能,因此,DLL的稳定性和稳定速度等问题比PLL要好。

◇ 总体电路结构设计

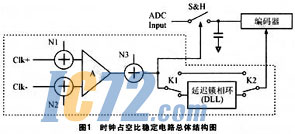

该时钟占空比稳定电路的总体结构如图1中的虚框所示,它由输入缓冲放大器A,开关K1、K2和延迟锁相环(DLL)组成。

当采样时钟频率低于DLL的工作下限时,开关K1、K2向上闭合,DLL被旁路;当开关K1、K2向下闭合时,DLL开始作用,并调节输入时钟信号相位,以使输入时钟的占空比接近50%,抖动小于0.5ps。

◇ 延迟锁相环(DLL)

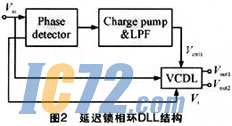

延迟锁相环(Delay-locked loop,DLL)的结构与普通锁相环(Phase-locked loop,PLL)相似,它只是用电压控制延迟线(VCDL,Voltage Control Delay Line)代替了压控振荡器。其结构框图如图2所示,一个普通的DLL包括4个主要模块:鉴相器、电荷泵电路、环路滤波器及VCDL。其中压控延迟线是由一系列电压控制的延迟可变电源串联而成的开路链,其输出信号是输入信号的延迟ntd。把压控延迟线的输入和输出送入鉴相器中进行比较,通过锁相环路使两者之相差锁定在一个周期(同相比较)或者半个周期(倒相比较),则每个延迟单元的延迟时间即为T/n或T/2n,其中n为延迟的级数。

DLL中的鉴相器的作用是鉴别相位误差并调节电荷泵的误差,以此来控制压振荡器的输出频率,常见的鉴相特性有余弦型、锯齿型与三角型,鉴相器可以分为模拟鉴相器和数字鉴相器两种,其主要指标有:

(1)鉴相特性曲线。也就是鉴相器的输出电压随输入信号相位差的变化曲线,该特性要求其为线性且线性范围要大。

(2)鉴相灵敏度。即单位相位差产生的输出电压,单位为v/raJ。理想鉴相器的鉴相灵敏度应与输入信号的幅度无关,鉴相特性为非线性时,一般将其定义为Pt=0点上的灵敏度。

(3)鉴相范围,也就是输出电压随相位差单调变化的相位范围。

(4)鉴相器的工作频率。

DLL中的电荷泵实际上是一个电荷开关,它可让相位的差异和超前滞后转化为电流,然后通过一阶电容的积分作用再转化成控制电压,然后用这个反馈控制电压来控制延迟时间,以使之达到所需要的相位延迟。

该DLL有两个作用:一是检测占空比;二是检测时钟抖动,由于延迟锁相是50%的时钟周期,因此当鉴相器(PDF)检测到占空比大于50%时,电荷泵(CP)往上使占空比降低,反之则往下使占空比上升 |