Tessera公司正式推出其MicroPILR封装技术,并声称该互连技术基本适用于多种芯片和板级应用。但观察人士对此论调持怀疑态度,认为该技术的成本和业界支持力度还不明朗。

Tessera最初将MicroPILR定位为一种可选的“封装堆叠(PoP)”技术,目标应用瞄准移动消费系统所用芯片。与目前使用的体积更大的传统焊接球相比,这种技术可以帮助芯片制造商在基底上封装更多的微型MicroPILR柱,从而有效节省空间,提高产品的密度和良率,Tessera公司表示。

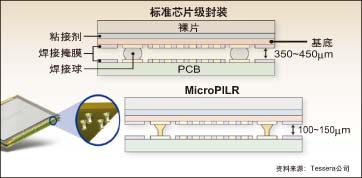

“我们认为该技术可以增加消费类和移动类产品的实际价值。”Tessera公司先进封装和互连部门高级副总裁Craig Mitchell指出。MicroPILR柱高度小于180微米,直径可在40-375微米范围变化。相比而言,焊接球的高度和宽度都在350-500微米范围之内。在焊接点间距方面,该技术可使裸片到封装的连接尺寸缩小至100微米、封装到电路板的连接缩小至0.3mm。

在一个使用4个DRAM芯片的例子中,MicroPILR堆叠高度为0.8mm,而传统的堆叠封装要2.15mm。

在另外一个演示案例中,Tessera用8个闪存芯片(每层两个芯片)创建了一个16GB的USB驱动器。最终形成的1.2mm闪存堆叠尺寸是一些竞争产品的一半。与当前的堆叠封装不同,Tessera的最新技术允许对每层进行单独的测试,潜在提高了良率。

Tessera表示MicroPILR技术还有其它诸多的好处。例如,它采用的镀镍铜柱差不多能使芯片的热导率提高10%。“铜是一种良好的散热体。”Mitchell指出。

MicroPILR技术无需使用测试槽,从而减少了测试槽在测试中可能引起的寄生现象。当用于PCB中时,MicroPILR柱可以缩短信号需要传输的距离,改善电气连接性能,并减少寄生现象。

图: MicroPILR封装技术瞄准更小、更密集的互连

MicroPILR技术需要新型蚀刻工艺以及一种新型铜/镍/铜材料,而其它技术则使用标准的封装设备和其它材料,Mitchell表示。MicroPILR正在接受至少4家芯片制造商的评估,不过还没有一家提出使用许可要求。

“我们采用的商业模型与我们的芯片级封装技术相同,即平均每个芯片交纳约2美分的版税,具体取决于互连的数量。”Mitchell介绍道。

但MicroPILR还需要得到基底制造商的支持,这在Tessera公司过去的封装技术中是没有的。有关这方面的许可条款目前还未公开。“传统基底无法满足我们的需求。”Mitchell表示。

Tessera希望芯片制造商在今年晚些时候能同意使用该技术。东芝公司半导体事业部执行副总裁Shozo Saito表示,东芝已经花了几个月的时间在堆叠闪存芯片中评估该技术,而且发现其“很有前途”。

MicroPILR技术源自日本North公司被称作Neo Manhattan Bump Interconnect(NMBI)的技术。追溯过往报导,Tessera与North就该技术的合作从2003年就开始了。在2005年5月时,Tessera完全买断了MicroPILR技术。

“我们与North公司联合开发的基底技术可以广泛用于各种封装应用,能显著提高产品的性能、功能和密度,同时降低成本。”Tessera主席兼首席执行官Bruce McWilliams在当时的一次讲话中表示。

Tessera正在开发用于PCB的新版MicroPILR,并预计于2008年发布,Mitchell透露道。

拭目以待

一些观察人士对该技术持观望态度,他们表示,近些年来,已经看到这种技术以不同形式出现。

“我还没有充分看到该技术的可制造性,从而无法判断其是否有很高的性价比。”专门从事封装问题咨询的Prismark Parters公司高级咨询师Brandon Prior认为。

被Delphi公司收购的Packard Hughes Interconnect公司也有类似技术,名为Microdot。“在一些概念上,两者类似,但Microdot采用了不同的制造工艺,而且目前还没有得到足够的发展动力。”Prior表示。

某封装公司的一位不愿透露姓名的执行官表示,他对该技术表示怀疑,其部分原因在于它需要被基底公司广泛采纳。“基底架构在全尺寸蚀刻连接方面,仍存在不少问题。”这位执行官指出。

“在亚洲使用这种技术批量制造PCB时,需要的是高良率和低成本。我没有看到Tessera针对这方面需求对技术架构进行任何改进。”他表示。

|