随着工艺尺寸的逐渐下降以及芯片复杂性的增加,如何在前段设计,即逻辑设计部分获得正确的时序信息,从而在时序、面积以及功率方面得到更好的平衡?如何在逻辑设计时准确预测实体层(即物理层)的具体信息?都成为前端逻辑设计工作者面临的难题。

事实上,在进行芯片设计时(见图1),在逻辑电路图中的给定区块内,所有的线路延迟(wire delay)都是一样的;但是在进行实际布局和布线时,元件之间的连线却发生了很大变化。在所有这些连线中,80-90%属于本地连线(local wires),也就是说元器件之间的线路很短,不会带来什么问题。但是另外10%的长绕线,通常却会产生严重的时序延迟,从而导致时序无法收敛。

当遇到这样的现实问题时,前端设计人员的典型做法,就是在综合时提出更严格的设计条件,对设计进行过度限制(over-constrain),这个数值通常达到30%。但是Over-constrain会直接导致芯片面积变大、栅容量增加,而针对于此,设计人员又不得不就栅容量的增加进行过功率(over-power)设计,这个数值甚至高达80%-90%,极大浪费了资源。

此外,面对当今尤为重要的低功率设计,时序收敛在其中的作用愈发重要。随着设计工艺由0.18um→0.13 um→90nm→65nm→45nm不断缩小,设计人员在进行电路合成时要考虑四大要素,它们分别是:面积优化、时序优化、MVT(multi-threshold)以及MSV(Multi-supply voltage)。这些都向EDA行业提出了更高的要求:需要及时提供满足多目标合成、多模式优化和分析、物理可预测的先进解决方案。

针对于此,Cadence近日在原有技术基础上,推出了最新更新的design with physical解决方案。

图1:Logical View vs. Physical View

Design with Physical方法

design with physical解决方案主要包括两部分:Cadence已交付使用的Encounter RTL Complier和First Encounter silicon virtual prototyping(SVP)。据Cadence设计系统公司亚太区技术市场经理Jack Chan介绍,此次Cadence的创新之处,就在于将First Encounter原本的 SVP功能带入Encounter RTL Complier综合环境中,从而使设计人员能够在综合环境中快速且正确地认识芯片级互联。(见图2)

图2:Design with Physical实现

为了在RTL-to-gate 逻辑架构过程中提供更好的互联模式,Cadence用PLE(物理布局预测)代替了线载模型(wireload modes)。(编者注:线载模型是根据扇出(fanout)的数目和一些简单的计算来估计布线负载,这种估计很粗糙,因为它忽略了扇出门(fanout gates)真正的实际布局位置,很难得到良好的综合结果),PLE使用物理库和floorplan信息,因而能够更正确地引导芯片中90% 本地连线的逻辑架构处理。而First Encounter的SVP部分,则是专门用来处理剩余10%长绕线的。

Jack介绍,Cadence最新Design with physical解决方案的推出,简化了芯片前端设计工程师的设计流程。在设计过程中,工程师可以在Encounter RTL Complier环境中首先呼叫PLE功能,进行电路合成;之后,通过简单的predict_qos指定调用First Encounter的SVP功能,与PLE一起,对设计进行分析和再优化。(见图3) 这样做之后能够更精准地预估到后端设计师所要的电路是否符合其时序设计要求。

图3:通过简单的predict_qos指定调用First Encounter的SVP功能

传统设计流程 vs. Design with physical

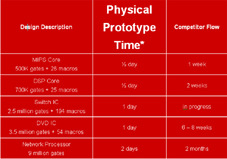

Jack在这里特别介绍了在一个定制化设计中,采用传统流程和design with physical解决方案所带来的不同结果,见图4:

“在传统流程中,电路合成只花4个小时的时间,”Jack表示,“但是这4个小时所产生的结果并不是最精确的结果,也可能时序很好,但是当把实体布线层放上去做优化的时候,发现结果并不是最满意的,落差非常大。我们看到图中出现的,这就是所谓的‘兵乓效应’,工程师需要反复才能得到最好的结果。”

图4:Design with Physical Speeds Feedback

确实,从图4可以看到,利用传统流程,前端工程师得到的结果往往与后端工程师的最终结果有很大出入,为什么会造成这种误差?Jack解释到:“因为在传统线路合成过程中,设计工程师往往会使用wireload model方法。而随着SoC的设计越来越复杂,靠wireload model无法解决线路布局的延迟问题。”

而与之相比,采用design with physical方法,虽然在最初合成的时候工程师花了7.5个小时,但是由于将物理层级概念带入了合成环境,因此最终得到的结果与前端工程师设计出来的结果非常接近,误差在1.3%,并且这样做可以极大节省整个设计所花费的时间(图5)。

图5:采用design with physical方法,极大节省了整个设计所花费的时间

|