����

LMS(��С����)�㷨���������ٶȿ켰�㷨ʵ�ּ��ص�������Ӧ�˲���������Ӧ��������������õ���ʮ�ֹ㷺��Ӧ�á�Ϊ�˷����㷨��������ܣ�������þ��д�̬��Χ�����㾫�ȵĸ������㣬��������������㲽��Զ�ȶ������㷱���������ٶ���������Ӳ����Դ������ӣ���˻��ڸ��������LMS�㷨��Ӳ��ʵ��һֱ������ѧ�����о����ѵ���ȵ㡣

����[1]�����һ���ʺ���FPGA(�ֳ��ɱ��������)ʵ�ֵ��Զ���24λ�����ʽ��һ�ָ�Ч�ṹ�Ķ�����FPA(����ӷ���)�����ֽṹ�Ķ�����FPA�봫ͳ�ļ����ṹ��Ȳ��������������ٶȣ����ܴ������������Ӳ����Դ��

�������ǻ������ָ�Ч�ṹ�Ķ�����FPA����FPGA�ϳɹ�ʵ���˻��ڸ��������LMS�㷨�����Խ��������ʵ�ֺ��LMS�㷨Ӳ����Դ�����١������ٶȿ�����������������ֵ�����

1 �������㵥Ԫ�����

1.1 ����ӷ��������

һ��˵����˫���븡��ӷ�����Ҫ���²������裺

a) �Խײ������Ƚ�ָ����С����ָ��С�IJ�������β��������λ��ʹ�������Ľ�����ͬ��

b) β����ӣ��ԶԽ��β�����м�(��)������

c) ��������Чλ���Ҹ�����λ�ķ����λ�������յĽ��롣

����FPGA���������źŴ�����ϵͳ�У�һ�㴦�������ݶ��Ǿ�A��D�����ͳ����źţ���ֱ���һ��ȡ12��16λ��ȡ18λ��Чλ�����������������������ͬʱ��ĿǰFPGA оƬ�ڼ��ɵij˷�������18��18λ��Ӳ�ˡ��ݴˣ�����[1]�Զ�����һ��24λ�ĸ������ݸ�ʽ����ͼ1��ʾ��

�ø�ʽ�ĸ���������ʾ�ľ���ֵ���������ͨʽ��ʾ��

ʽ�У�mΪ18λ��������

С���㶨�����λ��θ�λ֮�䣬����m����ʾ-1��1֮���С����eΪ6λ����������ΧΪ-32��31���ҹ涨��m=0��e=-32ʱֵΪ0��

��ͳ�Ķ����븡��ӷ����ṹ��ͼ2��ʾ����8����Ϊ������Ҫ7��˫����FPAͨ��3���������ɡ����ֽṹ���㷨��˳��ʱ�Ӻ��д������ظ����衣��3��˫����FPA�������3����ͬ�Ĺ�����������3���������1�����������棬�����ɴ����������ʱ�ӣ����ɼ�������Ӳ����Դ��

���ǻ��ڽ�FPA��һ�㲽��ֱ��Ӧ���ڶ�����FPA��˼�룬����[1]���һ��ȫ�µIJ����㷨����Ľ��㷨��8����ṹͼ��ͼ3��ʾ��

��ͼ3�У��������㵥Ԫ�����Ǵ�ͳ��˫����FPA�����Ǹ���FPA��һ�����㲽�蹹����㷨�ṹ��ͨ���������ò�������Ӷ�����С����ʱ�ӡ���8����ĶԽײ���Ϊ�����Ľ��㷨��8����Խײ���ֻ��˳�����3���Ƚϲ�����1������������1����λ����������ɣ�������ͼ2��ʾ�IJ����㷨������˳�����3���Ƚϲ�����3������������3����λ����������ڸĽ��㷨��˵������2��˳�����������2����λ����ʱ�ӡ�

1.2 ����˷��������

����˷����븡��ӷ�����ȣ�����Ҫ�Խ�ϵ�в�����ʵ��������Լ�24λ����˷����ṹ��ͼ4��ʾ��

���Ƚ��������ݵ�18λ����ֱ����˵�36λ�˷����������β����С���㶨�����λ��θ�λ֮�䣬��˽���ľ���ֵС��1���ʽ�ȡ��35��18λΪβ���˷������β���˷��������Ӻ��ָ��һ����й���������ɸ���˷����ܡ�

2 ����LMS�㷨��FPGAʵ��

2.1 LMS�㷨��һ�㲽��

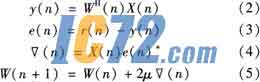

Widrow��Hoff��1960�������LMS�㷨������ȡ�����������ƽ�����ݶ���Ϊ��������ݶȵĹ��ƣ��㷨�IJ������£�

ʽ(2)��ʽ(5)�У�y(n)Ϊ����źţ�X(n)Ϊ����ʸ����W(n)Ϊ��ͷϵ��ʸ����r(n)Ϊ�ο��źţ�e(n)Ϊ����źţ���(n)Ϊ�ݶ�ʸ������Ϊ�������ӡ�

��ʽ(2)��ʽ(5)��֪��LMS�㷨������������ɼӷ����˷�������ɣ�����Ӳ��ʵ�֡��㷨������ʵΪ���ƹ�ʽ���Ҳ����жദ����ж�����ӷ����������������ø�Ч�ṹ�Ķ����븡��ӷ������ɴ�����ԼӲ����Դ����������ٶȡ�

2.2 �㷨��FPGAʵ��

���ø���LMS�㷨������Ӧ�����˲���������ʵ�֡������ź�Ϊ500 kbit��s��α������мӸ�˹������������Ƶ��Ϊ4 MHz����������Ϊ18λ���룬��7����ͷϵ������������ʽ(2)��ʽ(5)��֪������1��(ʽ(2))����2��(ʽ(3))����������貢�н���7���˷��������ٽ���һ��8����ļӷ���������3��(ʽ(4))Ϊ���н���7���˷���������4��(ʽ(5))�貢�н���7���ӷ����������и�ȡ2-5������˷�������FPGAʵ��ʱ������λ�������档

����LMS�㷨�ڲ�ͬоƬ��ʵ�ֺ��Ӳ����Դ����������1��ʾ��

���õĿ�������ΪISE7��li���������ΪVHDL���ۺϹ���ΪSynplicity7.0�����湤��ΪModelsim6.0��FPGA����ʱ��Ƶ��Ϊ64 MHz��

�ɱ�1��֪�����ڸ��������LMS�㷨����Ӳ����Դ���٣������ٶȸ�(���ʱ��Ƶ�ʴ���64 MHz)����������ϵͳ���Ҫ��

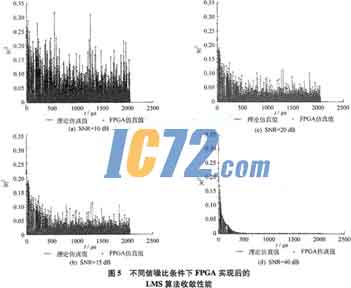

ͼ5Ϊ�ڲ�ͬ�����������FGPAʵ�ֺ�ķ����������۷������ĶԱ�ͼ����ͼ�п�����ؿ�������FPGA��ʵ�ֵĸ���LMS�㷨����������������ֵ�dz��ӽ���

3 ������

LMS�㷨��������Ȼʮ�ֳ��죬������LMS�㷨��Ӳ��ʵ�������㵥Ԫ��Ӳ����Դ���Ĵ������ٶ�����ȱ�㣬�Ӷ�һ���̶���������LMS�㷨����Ҫ���������źŴ��������е�Ӧ�á����ĸ�������[1]����ĸ�Ч����Ķ����븡��ӷ������ɹ�����FPGA��ʵ���˸���LMS�㷨��������Խ��������ʵ�ֺ��LMS�㷨Ӳ����Դ�����١������ٶȿ�����������������ֵ����� |