l 引 言

随着芯片规模呈现指数式的上升,验证能力已经远远落后于设计能力,并且正在成为制造功能更复杂、规模更庞大的芯片的瓶颈。第三届虚拟插座接口联盟就得出"验证不仅是非常棘手,而且是非常、非常棘手"这样一个结论。根据统计,数字系统设计的测试验证至少占据了70%的设计工作量,因此减少测试验证所花费的成本,提高测试验证的效率成为当前数字电路设计的关键;另一方面,电子器件的面市时间却要求以令人震惊的速度缩短,设计周期缩短的比其他任何细分市场都快。此外,日益流行的IP复用技术也使得传统的硬件描述语言(Hardware Description Language,HDL)仿真器难以胜任[1]。这些,都对现有的验证手段提出了严峻的挑战,同时也促使新型的验证思想和验证手段应运而生,硬件加速验证技术就是其中的典型代表。

硬件加速验证技术是指采用硬件仿真器对设计进行验证的方法和手段。硬件仿真器技术是基于处理器阵列或现场可编程门阵列(Field Programmable Gate Array,FPGA)这样的硬件平台,通过把待验证的设计映射到这些可配置、可编程的硬件上,然后对这样一个等效系统进行验证的方法。其主要特点有:

(1)方便用户在设计早期建立芯片的硬件模型;

(2)方便用户在设计早期调试芯片软件和设计; (3)可以处理的设计规模从5万门到2 000万门;

(4)在某些情况下该硬件模型可以按实时速度运行;

(5)硬件仿真器的可配置特点决定他可以多次重复使用;

(6)可以很方便地使用内置逻辑分析仪对电路进行调试;

(7)存在丰富的可复用的标准总线模型,如PCI,Ethernet等[2] 。

2 硬件加速验证系统的结构和工作原理

硬件加速验证系统一般含有3个主要的部分:系统管理工具、仿真软件和硬件加速器所用硬件平台,即硬件加速板,其组成结构如图1所示。

该系统管理软件负责协调软、硬件的工作分配以及完成对硬件加速板的操作控制;硬件加速板完成指定待加速模块的验证;仿真软件就是普通的HDL仿真器,如ModelSim,VCS,NC-Verilog等,产生硬件加速板所需的编译数据文件以及完成除在硬件加速板中加速仿真模块以外的各模块的仿真。

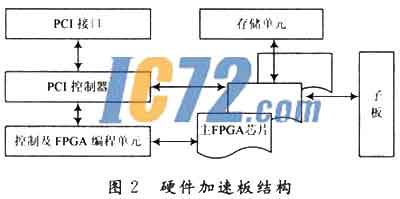

硬件加速板的典型结构如图2所示。硬件加速板一般至少含有2块FPGA芯片,分别供用户编程下载和系统控制用,即待加速模块被配置于硬件加速板中的主FPGA芯片中,而控制FPGA芯片控制对主FPGA芯片的动态编写。主FPGA芯片通过:PCI控制器与PCI接口相连,以实现和主机的数据通讯。硬件加速板通常还含有存储模块,如ROM,RAM,使得仿真时不再需要传统HDL仿真器所需要的仿真模型,大大提高了验证能力。为了使较大规模的电路也能在硬件加速板上实现仿真,一般的硬件加速板都含有子板的连接接口,子板可以是FPGA或是存储单元,也可以是ARM等微处理芯片,必要时可以通过添加子板的方式来增大仿真的门数或提高仿真的能力。

硬件加速验证系统的一般工作原理如图3第2~3行所示,而图3第1行所示实际就是传统的HDL仿真器的仿真步骤。 由图3可以看到,与传统的HDL仿真器在仿真器中完成整个仿真过程不同,硬件加速验证系统首先利用系统管理工具将HDL仿真器产生的编译文件通过接口任务,如PLI,FLI,VHPI等传递到硬件加速板的驱动,再由驱动将这些数据转化为硬件加速板所能接收的特定格式,这样待加速验证的模块便被配置到硬件加速板上的主FPGA芯片中,进而根据在系统管理工具中设定的仿真要求实现加速仿真。加速仿真结束后,与前述的过程类似,再由硬件加速板的驱动读取加速仿真结果,并通过接口任务传递到HDL仿真器中进行观测和调试,观测和调试的过程与传统的HDL仿真器一样。

由于将原本在HDL软件仿真器中完成的仿真任务下载到实际的硬件中完成,这类硬件加速验证系统能在很大程度上加快仿真速度,提高仿真效率。特别是针对较大规模的设计电路,这一效果尤为显著。这是因为随着设计规模的增大和运算复杂程度的提高,在传统HDL软件仿真器中的仿真时间基本是呈指数速度增加的,所以到了一定程度,其速度之慢,等待结果时间之长是无法忍受的。而在硬件仿真器中,无论设计的规模有多大,复杂度有多高,其运行时间相对于测试向量的运行时间是基本一样的。

3 现有商用硬件加速验证系统及其比较

正是由于硬件加速验证系统在减少大规模设计中仿真时间的突出性能,其在实际应用中也开始扮演越来越重要的角色。为了顺应市场的需要,各大EDA厂商也不断推出各具特色的硬件加速验证系统,主要有Mentor Graphic的VStation,Aldec的HES,Cadence的Palladium以及EVE的ZeBu等。

Mentor Graphic的VStation是业内最高端、性能最好的硬件加速验证系统之一。其专利Virtual-Logic综合技术及Virtual-Wires技术使得设计得以自动划分和综合到硬件设备上。VStation具有强大的分析和调试功能,提供了类似软件仿真器的调试界面,使得用户可以基于RTL代码进行调试。VStation设计容量大,可容纳多达30 M门的设计,并可以接受任何宽度和长度的数据流作为测试激励进行验证。

Aldec的HES采用增量原型技术,在每一个设计阶段都可以把设计下载到硬件中,随着下载到硬件中设计比例的增加,仿真速度越来越快。利用HES仿真的时间主要取决于在HDL软件仿真器上运行模块的速度,当整个设计全部被配置人HES时,所需要的验证时间基本上就是测试平台在HDL软件仿真器上运行的时间。

Cadence的Palladium是其推出的集成验证平台Incivise的主要组成部分。Palladium在一个统一系统下支持仿真加速和in-circuit仿效,并支持多用户和远程控制。

EVE的ZeBu采用FPGA和存储资源相互独立的技术来配置设计和可重构的测试平台,使得在新的激励下原有的设计不再需要重新编译,且只有修改过的FPGA部分需要重新布局布线。

4 基于硬件加速验证技术的验证流程

基于硬件加速验证系统的验证流程可以大致划分为编译、划分、综合、实现和调试等5个步骤,如图4所示(此流程基于Aldec的HES)[3]。为方便比较,图示上半部分即为传统HDL仿真器的仿真流程,由此可以直观地看出基于硬件加速验证系统验证流程的不同点。

(1)编译:这一步在HDL仿真器中完成。在这一步中,读入源程序和测试平台,完成对其的语法检查,产生编译结果文件,并将其转化为特定的数据格式供后续使用。

(2)划分:这一步在硬件加速验证系统的系统管理工具中完成。在这一步中,首先读入第一步产生的含有编译信息的数据文件。之后,根据实际需要分配软、硬件的仿真任务,即决定哪些模块是要在硬件加速板中进行加速仿真的,哪些模块是留在HDL仿真器中进行软件仿真的。典型的做法是将可综合部分放人硬件加速板中进行加速仿真,而将不可综合部分,如测试向量等留在HDL仿真器中进行软件仿真。合理的分配可以避免软、硬件的相互等待,对提高仿真效率有着重要意义。由于一般的硬件加速板上都含有存储器单元,故设计中的RAM,ROM等存储模块可以直接在硬件加速板中进行加速仿真,而不再需要传统的仿真模型。

(3)综合:这一步在硬件加速验证系统的系统管理工具中完成。在这一步中,调用预先设定的综合器,如Syplify,DC-FPGA,XST等对指定的待硬件加速仿真模块进行综合,产生门级网表(EI)IF格式)供下载实现。

(4)实现:这一步在硬件加速验证系统的系统管理工具中完成。在这一步中,调用适配下载工具(视硬件加速板的FPGA芯片而定,如Xilinx的ISE,Altera的Quartus等)对设计进行布局布线,并产生返回到HDL仿真器中进行调试的数据文件。

(5)调试:这一步返回到HDL仿真器中完成。在这一步中,执行上一步产生的数据文件(此文件实际上是一个批处理文件),完成加速仿真,最后进行观测、调试。 |