1 NANDFLASH

NAND写回速度快、芯片面积小,特别是大容量使其优势明显。页是NAND中的基本存贮单元,一页一般为512B(也有2kB每页的largepageNANDFLASH),多个页面组成块。不同存储器内的块内页面数不尽相同,通常以16页或32页比较常见。块容量计算公式比较简单,就是页面容量与块内页面数的乘积。根据FLASHMemory容量大小,不同存储器中的块、页大小可能不同,块内页面数也不同。例如:8MB存储器,页大小常为512B、块大小为8kB,块内页面数为16。而2MB的存储器的页大小为256B、块大小为4kB,块内页面数也是16。NAND存储器由多个块串行排列组成。实际上,NAND型的FLASHMemory可认为是顺序读取的设备,他仅用8b的I/O端口就可以存取按页为单位的数据。NAND在读和擦写文件、特别是连续的大文件时,速度相当快。

2 NANDFLASH与NORFLASH比较

NOR的特点是可在芯片内执行,这样程序应该可以直接在FLASH内存内运行,不必再把代码读到系统RAM中。NOR的传输效率很高,但写入和读出速度较低。而NAND结构能提供极高的单元密度,并且写入和擦除的速度也很快,是高数据存储密度的最佳选择。

这两种结构性能上的异同主要为:NOR的读速度比NAND快;NAND的写入速度比NOR快很多;NAND的擦除速度远比NOR快;NAND的擦除单元更小,相应的擦除电路也更加简单;NAND的实际应用方式要比NOR复杂得多;NOR可以直接使用,并在上面直接运行代码,而NAND需要I/O接口,因此使用时需要驱动程序。

3 NANDFLASH在系统中的控制

在没有NANDFLASH硬件接口的环境中,通过软体控制CPU时序和硬件特殊接线方式实现仿真NANDFLASH接口,进而实现在嵌入式系统中脱离NANDFLASH专用硬件接口进行对NANDFLASH读、写、擦除等操作的实现方法。

本方法主要工作在以下两个方面:

软件方面:针对特殊硬件线路的软体设计和严格的CPU时序控制;

硬件方面:硬件的线路设计,利用NORFLASH专用硬件接口控制NANDFLASH。

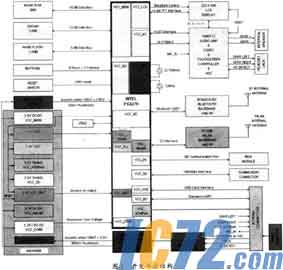

首先建立的开发平台如图1所示。

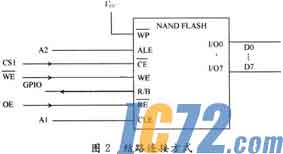

本平台使用Intel的PXA270Processor,无内建NANDFLASHController,使用NORFLASHController控制NANDFLASH,具体的线路连接方式如图2所示。

NANDFLASH的I/O0~I/07引脚用于对FLASH发送操作命令和收发数据,ALE用于指示FLASH当前数据为地址信息,CLE用于指示当前数据为操作命令信息,当两者都无效时,为数据信息。CE引脚用于FLASH片选。RE和WE分别为FLASH读、写控制,R/B指示FLASH命令是否已经完成。逭里选用的是CEdon'tcare的NANDFLASH。

NANDFLASH的读写操作以page方式进行,一次读写均为一个page,erase方式以block方式进行。这种方式,使其读写速度大大提高。

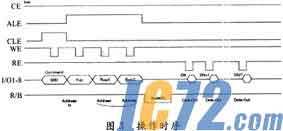

在时序方面,以读操作为例,其时序如图3所示。

操作过程主要分为以下几个步骤:

(1)发送读操作命令

CE有效,CLE有效,WE有效,I/O0~I/O8上面数据为command代码数据。

(2)发送地址数据(需要读取的FLASH地址)

CE有效,ALE有效,WE有效,I/O0~I/O8上面为所需地址数据。由于地址数据较多,所以需要分几次依次发送。每次发送都需要产生WE信号以将其写入NANDFLASH芯片。

(3)等待R/B信号,最后读出数据

在最后一个地址数据写入FLASH之后,R/B信号即变低。等待芯片完成整个page数据读取之后,R/B信号变高。此时,CE有效,ALE,CLE均拉低,依次产生RE信号,从I/O0~I/O8读取出所需数据。

对于写操作和擦除操作,其基本原理相同,只是信号顺序略有改变,就不再赘述。

由于使用了CPU地址线A1,A2连接CLE,ALE引脚,对CPU低2、3位地址的读写操作就意味着对NANDFLASH进行读写命令/数据操作。如果此程序工作在OS上的application层的话,MMU已经屏蔽程序对底层硬件的直接访问,所以需要对MMU进行设定,为NANDFLASH开辟一块。Memory映像区域,这样就可以通过OS对底层的NANDFLASH进行操作。以该系统为例,使用CPU的CS1引脚控制NANDFLASH的CE信号,先将其映像为0x24000000地址,此时,对0x24000000地址读写即对NANDFLASH芯片进行数据读写,而对Ox24000002地址写数据,使CPU的A1地址引脚为高,即对NANDFLASH发送command命令,同样,对0x24000004地址写数据,即对NANDFLASH发送address数据。

在对NANDFLASH发送命令/数据之后,由于程序运行速度比FLASH芯片快很多,需要在每一次操作之后插入若干等待周期,并利用CPU的GPIO检测芯片R/B信号。直至芯片完成本次操作再进行下一步操作。

需要注意的是,在对FLASH发送命令数据过程中的等待,没有反馈信号可以检测,只能通过反复调试确定其所需等待时间。

在设计中采用CPU的CS1信号对NANDFLASH进行CE(片选)控制。此处不能采用CPU的GPIO进行控制,因为在嵌入式设备的ARMCPU中,CPU本身采用了指令、数据自动预读的高速缓存技术和流水线技术。因此,当程序在NORFLASH里面直接运行的时候(目前绝大多数嵌入式系统采用的方式),在运行任何两段相连的代码中间,CPU都有可能对NORFLASH进行指令或数据的预读操作,从而产生大量的RE,OE信号和地址信号。如果使用GPIO控制NANDFLASH的CE信号则无法避免这种影响。CPU的CS1信号是由CPU内部自动产生,因此在CPU预读期间,CS1信号可以有效屏蔽NANDFLASH芯片。并且,由于NANDFLASH芯片支持CEdon'tcare模式,在CE无效的情况下,芯片本身的工作状态并不会被干扰,由此保证了NORFLASH和NANDFLASH在同一CPU界面中互不干扰的稳定运行。对于CS1信号的宽度等参数,也需要在实验中进行调节,才能保证整个系统快速稳定的运行。

4 NANDFLASH在系统中的读写速度

经过测试在该系统平台中,OS为PalmOS5.4;CPU使用PXA270312MHz;SDRAM使用Samsung的16bdatawidthHYB25L256160AF-7.5@104MHz;NANDFLASH选用Samsung128MB8bI/ONANDFLASHK9F1G08U0A达到在文件系统下面的读/写的速度为3MB/s,擦除的速度为65MB/s,在手持式设备中运用性能已经够了。 |