ժ Ҫ�� ͨ���Աȶ���FPGA���ݼ��ط�ʽ���ӿɿ��ԡ������Լ�PCB��Ƶȼ�������˵���˴��м��ص���Խ�ԣ�������Ŀǰ���м��������ٵ����⡣Ϊ������м��������ٵ����⣬����˲���EEPROM��9500ϵ��CPLD����ʵ�ִ��м��صĹ��룬��ͨ��ʵ����ƣ��ɹ���ʵ���˸ù��롣

�ؼ��ʣ� FPGA CPLD EEPROM ������ת��

�Դ��ģ�ֳ��ɱ�������������������Ⱥ����������������һ���ǻ���SRAM��ϵ�ṹ��FPGAϵ�У���XILINX��˾��4000ϵ�к����µ�Virtexϵ�У���һ���ǻ���faxtFLASH������CPLD��������XILINX��˾��9500ϵ�к�Lattice��˾��ispLSxxϵ��оƬ��FPGA���������������Դ�ḻ��Ƭ��ROM��RAM��������ص�1������������Ҫ��ÿ���ϵ�ʱ�������ݼ��ء�Ŀǰʵ�ּ��صķ������������֣��ٲ���PROM���м��أ��ڲ���ר��SROM���м��أ��۲��õ�Ƭ������ʵ�ּ��ء���һ�ַ�ʽ��Ҫռ�ý϶��FPGA�ܽ���Դ����Ȼ��Щ�ܽ��ڼ�����ɺ������һ��I/O�ڣ����ڼ���ʱ��������Щ�ܽ��������κ������ź�Դ���������ݴ洢��PROM��FPGA֮��Ĵ����̶�������8λ�������Լ���������PROM�ĵ�ַ�ߵȣ�ʹ��PCB��Ʋ��㡣���ǵ�һ�ַ�ʽ��һ�������ķ��棬��PROM�������ϴ������á��۸�͡�����֧��(�����)�Ϻá��ڶ��ַ�ʽ����պ����һ�ַ�ʽ�෴����ռ����Դ�١�PCB���巽�㣬��������С���۸�ϸߡ������Բ�����ַ�ʽ���õ�Ƭ�����ƣ���PROM�ж�ȡ�������ݣ�Ȼ���ٴ����ͳ��������漰����Ƭ����̣����ڿ�������˵��Ϊ���㣻���⣬�����Ƭ��������ʵ�ָ�����Ϊ�˷�Ӳ����Դ��CPLD��һ������ŵ��Dz��ü����ר�ÿ������ߣ�ͨ��JTAG��ֱ��һ����ʵ�ֱ�����ݼ��أ������ñ��������ǽ����ٴα��(��GAL��������)�����������Ƚ��ʺ���ʵ�����ڽ����ֳ����ԣ��������������ݵļ��ر���ͨ�����������˶��ڴ���Ұ����ҵ����˵��������㡣

ͨ�������Ƚϣ������ʵ�ʹ��������������Ϊ���ô������ݼ��رȽϷ��㡢�ɿ�(���ֿɿ��Ե�����FPGA��SROM֮����ٵĽӿ���)��������FPGA��ģ�IJ�����������CONFIG������Խ��Խ��ֹ������д��ʱ��CONFIG����������ѵ�6MBIT����ȻXILINX��˾����ص�XC17Xϵ��SROM�ṩʹ�ã�����Ϊһ����оƬ��2�������ɱ��ϸߡ������̹������ڳ����۸�ϸߣ����FPGA��Ӧ�ü��ռ������ܴ���ϰ���������ʹ�ù�AT��T��˾��ATT17ϵ�е�ɲ���SROM�����Ǹ���SROMоƬ����XILINXϵ��FPGAоƬʵ�ֽӿڵ�����࣬������С����������ԭ����۸�������ͬ���洢������EEPROM���塢�������������ߣ�������Դ���ѡ���ô�ܲ��ܽ�ϲ��м����봮�м��ص��ŵ㣬�Ӷ����������FPGA���ݼ��ص������أ���������ϸ�����˴��м��ػ��ƺ���Ϊ����EEPROM��Ϊ���ݴ洢���������ɿصIJ�����ת����Ӧ�ÿ���ʵ�����ݼ��ء�������XILINX��˾Virtexϵ��XCV100оƬΪ��������ATMEL��˾1��λ��AT29C010A�������ݴ洢������XILINX��˾9500ϵ��XC95108оƬ��Ϊ���ؿ�������������ơ�

1 ԭ�����

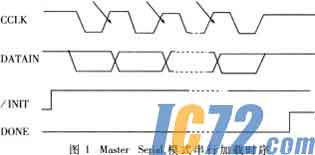

ԭ����Master Serialģʽ���м���ʱ����ͼ1��ʾ

�ڸü���ģʽ�У��Ƚ���Ҫ�ļ����ź�Ϊ/INIT��CCLK��DATAIN��DONE��/INIT��ʾFPGAоƬ�ϵ�ʱ���ߵ�/PROGRAM�ź�Ϊ��ʱFPGA�ڲ����ݳ�ʼ�����̣�����Ϊ�����źŸ����ݼ��ؿ���������Ϊ��λ֮�á���/INIT�ź�ԾΪ�ߵ�ƽʱ��CCLK��ʼ��������������DATAIN��CCLK�������ش��룬��ͨ�ô���ͨѶ�����ƣ�����������Ҳ�п�ʼλ�����λ����������֡�ķ�ʽ���ա�һ����������FPGA����ֹͣ�������ݣ�����/INIT�ź���Ϊ�͵�ƽ����˸��ź��ֳ�Ϊ����ָʾ�źš�������ȫ�����ܲ���֤�����FPGA��DONE�ź���Ϊ"1"��3�� �ڷ�����FPGA�������������Ժ��Եó�����һ�����ۣ���֤CCLK��DATAIN֮����ϸ�ͬ���������ԣ��Ϳ���ʵ�ּ��ء����ڴ˽��ۣ������ɼ������ݸ�ʽʱ��������ƬSROM���и�ʽ������XILINX��˾��FPGAϵ�У��ø�ʽΪ��MCS�ļ���ʽ��Ȼ����ALL07�������INTEL HEX���ݸ�ʽ����д��EEPROM�С����µĹ�������CCLK��/INIT��DATAIN�Ŀ�������ɲ�����ת�����ÿ��ƹ��̲���һƬCPLD֮95ϵ��XC95108оƬ���е�������������ϲ���һƬXC9536������ɣ�֮���Բ���XC95108����Ϊ������Ҫ�������������ԭ����ͼ��ͼ2��ʾ��

2 ������ת��ʱ�����

��ʱ������ϣ��ؼ�����Ҫ����DATAIN�������ݵ������ԡ�DATAIN��CCLK����ʱ�ӵ�ͬ�����Լ�EEPROM���ʵ�ַ�ĸ�λ���⡣���ڸ�λ���⣬�����ϵ�ʱFPGA������/INIT�źŶ�95108�ڲ���EEPROM��ַ��������λ����������ԭ����/INIT��FPGA֮CCLKʱ�Ӳ�������ͬ����ϵ����ͬʱҲĬ���ϵ������һ�γɹ����ڿ��Ǵ���DATAIN���ݵ�������ʱ������������λ�Ĵ������趨����ΪR_shiftA��R_shiftB����R_shiftA�ڽ�����λ����ʱ��R_shiftB��EEPROM�ж����λ�������ݣ���֮��Ȼ��Ϊ����DATAIN��CCLKʱ�ӵ�ͬ���ԣ�����������������CCLKΪͬ��ʱ�ӣ�ֵ��ע����ǣ�����DATAIN������������CCLK�������ش���FPGA��������Ǹ���XC95108оƬ��Ƶ���תʱ���Ǿ��������CCLKʱ�ӣ������ͱ�֤��CCLK��DATAIN��ʱ���ϵ��

������Ϊ�ü�����Ƶ�VHDLӲ�����������Ƴ������еļ���������λ�Ĵ���ģ����F2.11�������֮LogicBloxģ���������������F2.1I�����������桢����ɹ���JTAG��̵���д��XC95108оƬ���ӵ�����سɹ�������μӵ�ʵ�飬�ɹ���Ϊ100%��

��Ȼ�ó��������XCV100оƬ��AT29C010A EEPROM��Ƶģ�����������FPGA��EEPROMоƬͬ�����ã���ͬ������Բ�ͬ������EEPROM��Ӧ�ı����ַ��������λ����

Library IEEE;

Use IEEE��Std_logic_1164��all��

Use ieee��Std_logic_arith.all;

Use ieee��Std_logic_unsigned.all;

Entity v10sload is

port ��

pDATA�� in STD_LOGIC_VECTOR 7 downto 0����

Paddress inout STD_LOGIC_VECTOR 16

Downto 0����

CCLKIN�� in STD_LOGIC��

RESET in STD_LOGIC��

DATAIN��out STD_LOGIC

end v10sload��

architecture v10sload_arch of v10sload is

signal loadin CE Nce CCLK8 Nreset nCCLK aDATAIN��

bDATAIN std_logic��

signal clkenable CCLK std_logic��

signal ppDATA std_logic_vector 7 downto 0����

component clk_div8

PORT��

CLOCK��ASYNC_CTRL IN std_logic

CLK_OUT OUT std_logic����

end component��

component R_shift8

PORT��

D_IN�� IN std_logic_vector 7 DOWNTO 0����

LOAD IN std_logic

CLK_EN IN std_logic��

CLOCK�� IN std_logic��

LS_OUT OUT std_logic����

end component��

component BUFG

port I in std_logic�� O out std_logic����

end component��

begin

������������������������������������������

data��loading function statements here

nRESET����not RESET��

init_data��process��RESET��

begin

if RESET����0���� then

ppDATA������00000000�妠

else ppDATA����pDATA��

end if��

end process init_data��

L0 BUFG port map��I����CCLKIN O����CCLK

nCCLK����not CCLK

L1��counter17 portmap

��CLOCK����CCLK8��ASYNC_CTRL����nRESET

Q_OUT����pADDRESS

L2 clk_div8 portmap

��CLOCK����nCCLK��ASYNC_CTRL����nRESET

CLK_OUT����CCLK8

nCE����not pADDRESS��0

CE����pADDRESS��0����

clkenable������1��

L3��R_shift8 portmap

��D_IN����ppDATA��LOAD����nCE��CLK_EN����

clkenable��CLOCK����nCCLK

LS_OUT����aDATAIN

L4��R_shift8 portmap

��D_IN����ppDATA��LOAD����CE��CLK_EN����

clkenable��CLOCK����nCCLK

LS_OUT����bDATAIN

Process Adatain bDATAIN CE

begin

if CE����1���� then DATAIN����dDATAIN

else DATAIN����bDATAIN

end if

end process

end v10sload_arch |