引言

TMS320VC5470 (简称5470)是集成了基于TMS320C54x体系结构的DSP子系统和基于ARM7TDMI核的RISC微控制器子系统的CPU定点数字信号处理器。它与以前的器件相比,提高了速度、降低了功耗,并且在很大程度上提高了编程灵活性,有利于对产品的软硬件升级,用于实现具有特殊功能的产品。通过合理安排软硬件资源,还可以节省投资,加速上市时间。

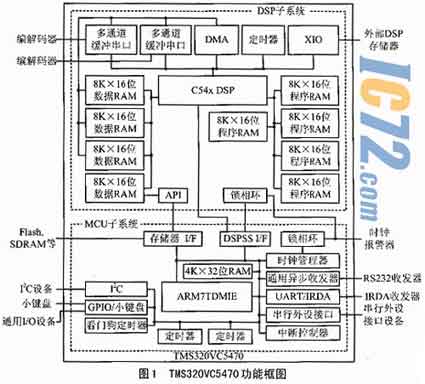

1 TMS320VC5470特性及功能框图

*集成了1个TMS320C54x体系结构的DSP和1个ARM7TDMI RISC MCU的双CPU处理器;

*带有72K×16位集成SRAM的16位低功耗DSP,速度可高达100MHz;

*用于DSP和MCU子系统的先进电源管理和低功耗模式;

*集成的DSP子系统外围,包括2个高速的全双工多通道缓冲串口McBSPs,使DSP核可以与编解码器(CODEC)直接接口;具有6个独立通道的DMA控制器;ARM端接口(port interface)为MCU子系统和DSP子系统的CPU之间进行有效的信息交换提供了2K×16位的共享存储器接口;外存储器接口EMIF(External Memory Interface);可以将外部总线周期扩展到14个机器周期的软件可编程等待状态生器;1个用于控制功能的软件可编程的硬件定时器;可编程的锁相环PLL时钟发生器。

*带有16K字节集成SRAM和仿真性能增强型的ARM7TDMI RISC微控制器核,使运行速度可高达47.5MHz;

*集成的MCU子系统外围,包括通用异步收发器UART、支持SIR协议的UART/IrDA接口、串行外围接SPI、36个通用I/O引脚、I2C接口、 2个通用定时器、1个看门狗定时器、中断处理器、支持Flash/SRAM/SDRAM/ROM的外部存储接口、对MCU外围灵活的时钟管理、可编程的锁相环时钟发生器。

*基于片上扫描的仿真逻辑,DSP和MCU核的IEEE标准1149.1+(JTAG)边界扫描逻辑;

*支持DSP和MCU核的基于扫描的仿真。

图1为TMS320VC5470器件的功能框图。此器件由DSP和MCU 2个子系统构成。

2 DSP子系统功能介绍

DSP子系统是基于TMS320C54x、片上存储器和外围的,并且与其它的C54x产品代码兼容。DSP子系统包括DSP CPU核、用于产生时钟的锁相环、与外部并行设备连接的接口、1个定时器、72K字的RAM、2个多通道缓冲串口、1个允许MCU访问DSP子系统某部分存储器映射的接口以及1个JTAG接口。

(1)DSP核

5470 器件中DSP子系统的定点数字信号处理器(DSP)采用的是先进的改进型哈佛体系结构,其中有1条程序存储器总线和3条数据存储器总线。此处理器提供具有高度并行性的算术逻辑单元(ALU)、专用硬件逻辑、片上存储器以及附加的片上外设。DSP操作的速度和灵活性的基础是其高度专用性的指令集。

程序和数据空间的分离以及4条并行总线允许对程序的指令和数据进行同时访问,每条总线访问不同的存储器空间以实现不同的DSP操作,从而提供了高度的并行性。在1个单周期中可以执行2次读操作和1次写操作。并行存储的指令和特定应用的指令可以完全利用这种结构。另外,数据可以数据和程序空间之间进行传输。这种并行性保证了包含算术、逻辑和位运算的强大的操作指令集都可以在1个机器周期内完成。DSP子系统还包含1个专门用于在线仿真的仿真端口,此端口直接被TI公司的扩展型开发系统(XDS)硬件仿真器访问并提供仿真。除此之外,5470的DSP子系统还包括控制机制,用于管理重复操作、函数调用和DSP 中断。

(2)DSP存储器

5470 器件提供72K字的片上RAM如下:40K字的程序空间单边访问RAM(SARAM)、16K字的数据空间双边访问RAM(DARAM)和16K字数据空间单边访问RAM(SARAM)。每一个DARAM块可以在1个机器周期内执行2次DSP访问。DSP子系统在1个机器周期内还可以执行对分离的存储块的多个访问。在一次正常的复位之后,地址0x0000~0x7FFF之间的数据空间RAM块只被映射为数据存储空间,址0x06000~0x0FFFF之间的程序空间RAM块只被映射为程序空间。DSP存储器映射有2种模式:正常模式和API启动模式。复位、中断和陷阱向量均位于程序空间。当出现陷阱时,处理器将陷阱地址加载到程序计数器(PC),并从这个向量位置开始执行代码。器件复位后,复位、中断和陷阱向量映射到程序空间的地址FF80h。然而这些向量可以通过加载中断向量指针(IPTR)重新使之映射到程序空间中的任何128字页面的开始地址。

(3)DSP寄存器

5470器件有27个寄存器映射的CPU寄存器(MMR),它们映射到地址为0H~1FH之间的数据存储器空间。此器件还有1个与外围相关的存储器映射的寄存器组。

5470 器件的分体切换控制寄存器BCSR(Bank-Switching Control Register)既控制着与5409类似的分体切换等待状态的发生,也控制着5470的一些特性。分体切换等待状态,指DSP子系统交叉访问程序或数据存储器空间内的存储器分体边界时,自动插入1个周期。当交叉访问数据空间和程序空间的边界时,也会自动插入1个分体切换等待状态。BSCR所控制的 5470的特性包括对一些DSP子系统外存储器接口功能配置的控制,以及一些有关MCU可以用来访问DSP子系统某RAM部分接口的内容。BSCR寄存器还为DSP提供了些对ARM编程接口的控制,这一机制使得MCU可以访问数字信号处理器的内部RAM部分。此外,还包括对API模式(APIMODE 位)、1个MCU中断(HINT位)、DSP存储器映射选择(ABMDIS位)的控制。图2给出了BSCR寄存器的位结构,表1列出了各字段的功能。

表1 分体切换控制寄存器位字段的功能

(4)DSP外围

DSP子系统提供了与5409类似的高速全双工串口――2个多通道缓冲串口(McBSPs)。它们允许与其它的54x设备、编解码器及系统中的其它设备进行直接接口。

DSP子系统包括1个6通道的DMA控制器,用于执行独立的数据传输。在DMA控制器进行DMA传输时有几点限制;第1,DMA控制器能访问通常在程序空间的 RAM,不能访问在MCU子系统中执行的RAM,不能访问在DSP数据空间与API接口连接的RAM;第2,DMA控制器不能在McBSP DRR和DXR寄存器之间进行数据传输,不能在McBSP DRR或DXR寄存器与外部资源之间进行数据传输;第3,DMA控制器不能对外部资源进行32位的访问。

MCU和DSP之间通过片上共享的API存储器进行信息交换。API存储器是一个8K×16位字的DARAM(Dual-Access RAM)块。API存储器还可以被DSP用作通用数据或程序DARAM。在这个电路中,只有DSP存储器有DARAM。API通过分体切换控制寄存器可以选择两种操作模式之一:共享访问模式SAM(Shared-Access Mode)和主机模式HOM(Host-Only Mode)。在SAM模式下,DSP和MCU都可以访问API存储器。来自MCU的异步主机访问在内部被重新同步。如果DSP和MCU试图在同一时间进行访问操作,那么MCU进行优先访问,而DSP则等待1个周期。当DSP处于IDLE1模式时,SAM可以运行。在HOM模式下,只有MCU可以访问API 存储器,对于DSP则禁止读访问。当DSP从一个复位相退出时,缺省配置是SAM模式。当DSP处于正常操作模式或IDLE1模式时,通常选择SAM模式;当DSP处于IDLE2或IDLE3模式时,通常选择HOM模式。

(5)DSP电源管理

DSP 子系统具有3种省电模式,分别由IDLE1、IDLE2和IDLE3指令激活。在这种3种模式下,C54x DSP核进入睡眠状态,从而与正常模式相比大大降低了功耗。这3种模式的区别于对芯片内部模块的关闭程序及唤醒方式不同。在IDLE1模式下,关闭除 DSP系统时钟以外的所DSP活动。因为系统时钟要用于DSP子系统外围模式,所以DSP外围电路能够继续工作。这样,外围(例如串口和定时器)则可以命名DSP离开省电状态。在IDLE2模式下,同时关闭DSP子系统的外围及DSP核,但是DSP子系统的锁相环(PLL)时钟放大器则仍将保持活动状态以便可以从IDLE2状态快速恢复。由于DSP子系统的外围在这种模式下被关闭,它们不能像IDLE1那样通过产生中断来唤醒C54x。然而,由于外围的完全关闭使功耗大大地降低了。为了终止IDLE2,可以通过复位或激活中断0来实现。IDLE3模式与IDLE2模式类似,只不过它还将关闭锁相环(PLL)电路。IDLE3用于获得最小可能的DSP功耗。另外,如果系统要求C54x运行在较低的速度下以节省功耗,那么IDLE3状态允许外部重新配置DSP PLL。与IDLE3一样,通过复位或激活断0可以终止IDLE3。

3 MCU子系统功能介绍

5470 MCU子系统包括TI公司的增加了仿真特性的ARM7TDMI微处理器核以及一些外围,包括SPI和I2C接口、通用异步收发器、定时器、通用输入/输出接口和外部存储器接口。MCU子系统提供4K×32位的通用RAM和4K×32位的太网包RAM。

(1)MCU核

MCU子系统使用TI公司的增加了仿真特性的ARM7TDMIE核,它是ARM公司ARM7TDMI核的一种衍生品。ARM7TDMI处理器核是ARM7 Thumb家庭中的一种,是一种低功耗3的32位RISC处理器,并且组合了Thumb 16位的压缩指令集。这种微处理器可以通过执行中2位或16位指令来处理32位、16位或8位数据。由于引入Thumb而获得的卓越的代码密度,可以降低对存储器大小的需求,并且可以从16位宽的存储器获得32位的系统性能,从而降低了系统的成本。

MCU存储器空间包括内部RAM、内部外围、用于访问外存储器和外区域以及外部SDRAM。

(2)MCU存储器接口

MCU存储器接口通过1条32位宽的数据总线使MCU与内部及外部的存储器和外部设备连接。这条总线支持MCU访问8位、16位和32位的数据。所有的外围控制寄存器均为32位,因此只能使用32位的操作进行访问。

MCU存储器接口允许端配置,以便保证所有的外部设备工作在同样的端模式下。MCU存储器接口还提供对外部访问的管理,所支持的外部设备包括ROM (Flash)、SRAM和SDRAM。外部数据部线是一种32位的双向总线。MCU对内部外围和内部存储器的访问通常在0等待状态执行。SDRAM刷新周期使任何MCU访问发生延迟。MCU对外部SDRAM存储器访问的定时由SDRAM接口寄存器控制。

API接口用于MCU对DSP存储器中的某一小部分进行访问,它提供了一条通向DSP子系统中的API RAM的16位数据通路。所有的32位事务被分成2个16位的API事务。API接口支持向连续的访问操作之间可编程地插入等待状态,以保证MCU子系统和DSP子系统之间的信号同步。

(3)MCU外围

5470MCU子系统的外围主要包括通用异步收发器(UART)接口、串行外围接口(SPI)、通用I/O口、I2C接口、定时器和中断控制器。

UART 模块通过2个64位深的先进先出堆栈对处理器接收到的字符数据执行从串行到并行的转换,并对处理器传输的字符数据执行从并行到串行的转换。SPI是一个双向的3路接口,用于为从或向外部设备进行的数据传输提供一个3路串行接口。这个串口完全由MCU存储器接口控制。它是基于一个循环移位寄存器的,允许2种传输模式,即并行输入、串行输出和串行输入、并行输出。54703提供36个通用I/O口(GPIO),它们可以通过内部寄存器配置成读或写模式。这些 GPIO被分成2组:GPIO(19:0)和KBGPIO(15:0)。KBGPIO是键盘GPIO引脚,它们当中有些具有内部上拉电阻,但其进行的操作与GPIO(19:0)引脚类似。主I2C接口模块为MCU子系统总线和I2C引脚之间提供了1个接口,它允许MCU控制与I2C引脚连接的外部设备。 I2C接口实际上一是个并行到串行和串行到并行的转换器。从MCU接收的并行数据必须在I2C总线上转换为适当的串行格式传输给外部设备,从I2C总线上接收的串行数据必须转换为适当的并行格式传输给MCU。5470 MCU子系统包括3个16位的定时器,它们可被配置为“自动加载”或“倒计数器0并停止”2种模式。当定时器计数到0时,向MCU产生1个中断。定时器0 可被配置为看门狗定时器或通用定时器,定时器1和时器2为通用定时器。看门狗定时器在倒计数为0时复位MCU子系统,以避免用户程序被死循环阻塞而使程序失去控制。MCU子系统的中断控制器对MCU子系统的16个中断源(IRQ0~15)进行优先权和屏蔽控制。它还可以将这些中断划分为MCU的2种中断输入:nIRQ(低优先级中断请求)和nFIQ(快速中断请求)。它既可以从内部模块也可以从外部的芯片环境中接收中断。外部中断可以通过GPIO和/或 KBGPIO引脚提供。

(4)MCU的省电模式

MCU及其子系统外围可以通过设置CLKM_BER和WAKEUP_REG2个寄存器的适当位被关闭和唤醒。在MCU关闭之间,由软件来负责将ARM_CLOCK设置为旁路或低频模式。由来自某外围的第1个中断将MCU唤醒。

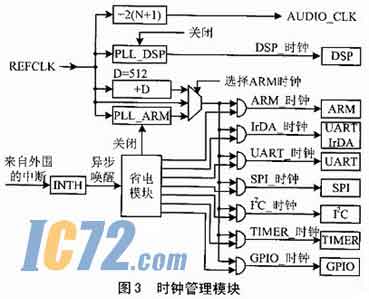

(5)MCU外部时钟管理

5470 器件由外围时钟输入信号REFCLK提供时钟定时。5470 REFCLK输入不提供时钟振荡器。所以它必须由遇到VIH和VIL请求的方形波输入信号来驱动。DSP和MCU子系统的时钟都是通过使用锁相环由 REFCLK衍生的。复位或加电之后,2个子系统中各自CLKMD寄存器内容由各自锁相环上可编程内部端口的状态决定。对于MCU子系统,这些内部端口是硬连线的,所以缺省模式下的可编程性能是不可用的。对于DSP子系统,DSP PLL的可编程内部端口与寄存器DSP_REG的输出相连接,此寄存器由RISC处理器控制。这样在MCU子系统的控制下,DSP PLL的缺省值则允许为可编程的。图3为时钟管理模块框图。

MCU子系统有3种运行模式:PLL(正常情况下)模式、DIV模式和省电模式。在省电模式下,输入时钟频率被一个大数(512~1023)相除。当把 MCU子系统时钟模块配置为省电运行模式时,如果使用一个小于512的值做除数,则将导致时钟停止。与DSP时钟相似,MCU子系统时钟也是由输入时钟(REFCLK)的扩展版本衍生的。RISC使用的PLL与DSP PLL一样,因此,RISC处理器使用与DSP相同的最小输入时钟频率限制和扩缩值(scalingvalue)。

(6)初始化

RESET 是复位DSP和MCU子系统的主复位输入。RESET_OUT信号在MCU的控制下可用于复位外部设备。当MCU子系统被复位时,MCU程序计数器从地址 0x00000000开始执行;当DSP子系统被复位时,DSP程序计数器从地址0xFF80开始执行。每一个MCU子系统外围可以通过MCU子系统寄存器RESET_REG的控制位被独立地复位。缺省情况下,只要MCU子系统复位一被激活,这些位就被置位,从而使所有的MCU子系统外围处于活动状态。

5470 提供了灵活的仿真性能。它既支持TI公司的仿真工具,也支持第三方公司开发的工具。由于这些仿真工具可能既识别C54x DSP核也识别ARM7TDMIE核,也可能只识别C54x DSP核,或只识别ARM7TDMIE核,或只识别ARM7TDMI核,因此需要多种仿真模式。为了允许对各种仿真器使用的内部JTAG链进行配置, 5470在TRST的上升沿对EMU1和EMU0引脚进行取样。根据这些引脚的值,内部扫描链被配置成不同的仿真模式。

结束语

自20 世纪80年代数字信号处理器进入市场以来,在社会各个领域得到了迅速广泛的展。从通信、网络、雷达等领域到马达控制、数码相机、助听器领域都在使用数字信号处理器。由于TI公司最新推出的双核定点数字信号处理器TMS320VC5470具有双CPU、功耗小、速度快等特点,为数字信号处理领域提供了一种更先进的可选器件。希望通过本文的介绍,可以使硬件或软件工程师在选用此器件进行应用开发方面有所帮助。 |