1引 言

移相电路在现代通讯技术、波形调制和雷达扫描等许多方面有着大量的运用。目前实现方式大致可分为模拟和数字2类。模拟移相器的电路较为复杂、线性差、响应时间慢,抗电磁干扰能力差。而数字移相器主要分2类[1]:第一类是运用直接数字式频率合成技术DDS。另一类是利用单片机计数延时的方法实现。其中使用DDS的移相器的实现精度大多依照"360°/2°"的方式实现,即其能够实现180°,90°,45°,22.5°,11.25°等精度[2]。另外其实现电路也较为复杂;而第二类利用单片机虽然可以实现较高精度的移相,但使用的单片机属于硬核IP[2],在大规模集成和使用权问题上十分不方便。本文介绍的基于可编程数字控制方法的移相原理,其精度可以通过精度控制输入信号任意赋予(在本文中精度调制为1°来说明)。此原理的电路采用采样电路和精度为1°的360倍倍频器等进行延时输出波形,方法简便,电路结构简单,能够配合任意工艺特性加以实现,且能够方便地集成到大规模电路中去。

2基本原理

本系统是基于数字倍频器进行延时操作而实现的移相。实现原理是把输入模拟波形(如正弦信号)的周期Tin转化为原来的1/data,Tin/data即为移相精度,data值通过精度控制输入信号赋值。当data为360时,精度为1°;当data为720时,精度为0.5°;若要更小的精度,可依此类推。本文中为便于显示移相波形,把精度设置为1°。则精度为Tin/360,所用的倍频器倍频因子即为360。这样经n个Tin/360延时(n为移相的具体数值,由记时控制输入信号D赋值),再输出波形。和原波形相比就形成了移相。从实现的电路方面来讲,要把输入波形周期变为原来的1/360,或者说把输入波形的频率变为原来的360倍,最直接的办法就是采用倍频器。而数字倍频器的输入是数字信号,则应先把模拟量转化为数字量,这就需要一个模拟比较器。在得到倍频输出信号后,为了要得到希望的n值,还应在倍频器后添加数字定时输出计数器,以输出延时控制信号。最后把模拟信号输入A/D电路,通过ROM存储,再在延时控制信号的作用下延时输出数字量,再经过D/A电路还原为模拟量,最终实现移相操作。其中倍频器具有360倍倍频能力。

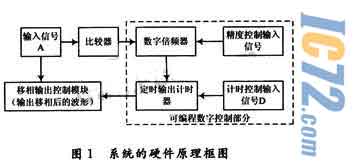

输入模拟信号(如正弦波)经过信号比较器,波形电压与零伏比较后,高于零伏的电压段转化为高电平,低于的转化为低电平,这样输入信号就转化为周期相同的数字信号。A/D,ROM,D/A和一些控制电路构成移相输出控制模块。其中移相控制部分的倍频器,定时输出计数器构成可编程数字控制部分,都可以通过硬件语言编译实现。这样得到的系统硬件原理框图如图1所示。

以下着重说明数字倍频器、数字定时输出计数器和数模混合输出控制电路。

2.1数字倍频器

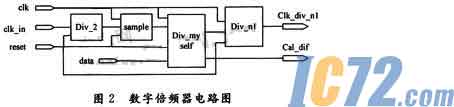

这里使用的数字倍频器(电路如图2所示)的算法是基于采样的原理来实现[4],理论上能够实现任意倍倍频,这里为方便说明和显示波形,设置为360倍,即倍频因子为360,精度为1°。

当信号A经过比较器后,A转化为具有相同周期的数字信号DA,他们的周期均为Tclk_in。通过引入高频时钟信号(其周期为Thf_clk)采样,以此来计数在一个Tclk_in中含有的Thf_clk的个数,把这个结果记为Nhf。则有:

Nhf=Tclk_in/Thf_clk (1)

由于倍频因子是360,所以对于倍频后的结果clk_div_n1有:

Nhf_of_clk_dive_n1=Nhf/360 (2)

Tclk_div_n1=Nhf_of_clk_dive_n1×Thf_clk (3)

Tclk_div_n1为倍频后倍频器输出波形的周期,Nhf_of_clk_dive_n1为一个Tclk_div_n1中含有的采样信号周期的个数。

联立式(1),(2),(3),可得:

Tclk_div_n1=Tclk_in/360 (4)

亦即:

fclk_in×360=fclk_div_n1 (5)

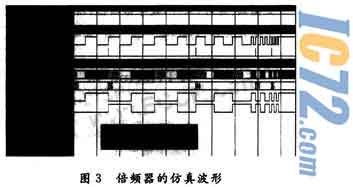

从而实现了360倍倍频。Tclk_div_n1就是信号A相移27π/360(即1°)时所占的时间间隔。图3是本倍频器的仿真波形(这里把倍频因子固定为360)。在每次输入信号周期变化后,都按照新的周期进行360倍倍频

这里应说明的几点是:

(1)如图2所示,data就是精度控制信号,不难看出,实际上他也就是倍频器的倍频因子。当data=360时,移相精度为1°。那么当倍频因子改变时,移相精度随之而改变。若data为720,则移相精度为0.5°;若data为3 600,则移相精度为0.1°。这些都可以通过改变精度控制信号data来实现,从而达到精度可变的目的。

(2)reset为复位信号,在输入信号DA(也就是电路图中信号clk_in)时应先复位。

(3)从图3可以看到,每隔一个Tclk_in,Nhf就会被重新计算一次,并与上次的结果作比较,这样输出信号cal_dif会在输入信号clk_in的周期发生变化时(也就是两个Nhf数值不一样时),输出一个高电频。这个高电频就是下两个模块数字定时输出计数器和数模混合输出控制电路中一部分模块的复位信号,从而达到倍频器输出信号周期自调节的目的。

(4)式(1)~式(5)的推导实际上都忽略了除法中的余数问题。当式(1)除不尽时要考虑余数的四舍五入问题。式(2),式(4)应修改为:

Nhf_of_clk_dive_n1=Nhf/360 (6)

Tclk_in=360×Tclk_div_n1+R (7)

其中,R为倍频后的时间余数,RN是倍频后的计数整数的余数,他们是同一概念的2种表述.对余数四舍五入的实现方式是先把Tclk_div_n1作二倍频处理得到Tclk_div_n2。以Tclk_div_n2对输入周期Tclk_in再次采样后得到值N。按照理想无余数的情况考虑,N应该是720。但当余数存在的情况下,若N大于720,则说明,RN≥0.5。那么表示倍频器的输出结果Tclk_div_n1的式(3)应修改为:

Tclk_div_n1=(Nhf_of_clk_dive_n1+RN)×Thf_clk (8)

当RN≥0.5时,按四舍五入考虑,可得:

Tclk_div_n1=(Nhf_of_clk_dive_n1+1)×Thf_clk (9)

若N没有大于720,则说明RN<0.5。那么就按照式(3)处理;否则应该按照式(9)处理。

2.2 定时输出计数器

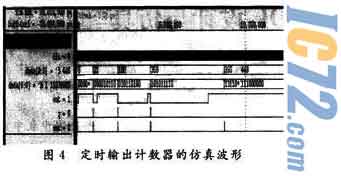

定时输出计数器的输入有计数数据data(9位)、复位信号set、数据输入加载信号q和clk,输出out.其中clk接倍频器输出信号clk_div_n1。定时输出计数器的仿真波形如图4所示。计数器的复位分2种情况;首先是倍频器的输出信号cal_dif引起的复位;然后在输入新的数据data时,由q引起的复位。由于数据data是9位,则仅当D<101101000(即10进制的360)时,q才引起复位。否则不复位,数据也不加载。当计数器复位后,out为0,在data个周期后,out输出高电平。如仿真波形图4所示,每输入一个小于360的数,则输出信号变为低电平,直到延迟时间结束后输出高电平。

2.3输出控制模块

输出控制模块的主要作用是波形保持。先保持两组波形一致,即先在模拟输入信号输入A/D[5,6]转换电路后,得到的数字量同时输入到两个相同的ROM中存储。在这个过程中倍频器一直处于复位状态。在ROM中存储完一个输入信号局期后,给一个信号使倍频器停止复位,开始正常工作。ROM1在计数器开始运作时就开始循环输出数据。ROM2在响应完延时信号后循环输出数据。其原理框图如下:

3 最终仿真波形

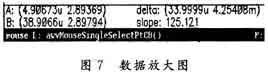

这里的A/D电路是10位逐次逼近型电路,输入信号周期为720 μs,时钟工作频率为5 MHz,每隔11个时钟周期采一次样。应根据采样的次数确定ROM的大小。这里的输入模拟信号周期为720μs,A/D时钟周期为0.2μs,共采样300次,每次10位数,则这里需要4 k的两个ROM。ROM2的输出由定时输出计数器控制。这里假设相移要求为17°,则其时间延迟Tdelay=17×Tclk_div_n1。最终仿真波形如图6,图7所示。

图7是图6左下角数据的放大。这是由Cadence 公司的仿真软件Spectre仿真计算得到。在图6中,上面的波形为原来的正弦输入信号;中间的是不经过移相而直接输出的结果;下面的是移相后的波形。由软件显示计算2个波形的时间差为:TB-TA=38.9066μs-4.90673μs=33.999 9μs△34 μs。根据本文介绍的延时控制理论,延时的数值应为:TDelay=17×(720μs/360)=34μs。由此可见,仿真后得到数据和理论数据完全吻合,从而证实了本文原理的正确性。

4 结 语

通过上面论证,文中移相器的精度理论上可以任意定义。倍频器在因温度等外界因素导致输入信号A的周期发生变化时,能立刻自我调整,使输出与输入的关系恒定(即fclk_in×360=fclk_div_n1),并能够根据外部输入信号A的周期变化进行自我调节适应,另外对倍频后的时间余数进行了四舍五入处理,因而具有精度高,失真度小的特点。如果调整工艺,并使用性能较高的比较器,那么还可以使得移相器的输入信号频率大大提高,从而满足高频电路的移相需要,拓宽了应用领域。同时本移相器除了适合正弦信号外,还适用于三角波信号和其他模拟信号的移相。 |