TMS320VC5402�����¼��C5402���ǵ���������˾��TI��1999��10���Ƴ����Լ۱ȼ��ߣ�Ŀ��۸��Ϊ5��Ԫ���Ķ��������źŴ�������DSP����

C5402��Ҫ�ص�����[1]��

*�������ʴ�100MIPS��

*�����Ƚ��Ķ����߽ṹ������16λ���ݴ洢�����ߺ�һ������洢�����ߣ�

*40λ��������Ԫ��ALU��������һ��40λͰ����λ��������40λ�ۼ�����

*һ��17��17�˷�����һ��40λר�üӷ���������16λ�����������ŵij˷���

*����ά�رȼ��������������ά�رȱ�������ٶȣ�

*���������滯��ָ�����룻

*8�������Ĵ�����һ������ջ������ʹ��ҵ�����Ƚ��Ķ���DSP �����Ա�������

*���ݣ�����Ѱַ�ռ�1M��16bit������4K��16bit ROM��16K��16bit RAM��

*���ÿɱ�̵ȴ�״̬�������������PLL��ʱ�Ӳ�������������ͨ�����崮�пڡ�һ��8λ�������ⲿ������ͨ�ŵ�HPI�ڡ�2��16λ��ʱ���Լ�6ͨ��DMA��������

*���ģ�������Դ��3V��1.8V���ںˣ����ر��ʺϵ�ع����豸��

�ɴ˿ɼ�����TMS32054Xϵ�е�����оƬ��ȣ�C5402������еĸ����ܡ����ĺ͵ͼ۸����ԣ�ʹ��һ�Ƴ����ܵ�ҵ���û��Ļ�ӭ���������ڲ��ṹ��Ƭ����ģ������װ�أ�Bootloader��������C54��ϵ�е�����DSP������[2]�нϴ�IJ��죬������Ӧ�ö����ִ����Ҫ�����ѻ����У�������У�STB����������������(PDA)����������ͨ�ŵ���Ƕʽϵͳ��Ϊ�ˣ������������ǵ�ʵ�����飬����C5402 Bootloader���������ʵ�ַ���������Ϊ��ϸ�ؽ��ܲ���I/O Bootloader������

�� ��������װ�ط���

C5402 Ƭ����ģ��Bootloader�������ϵ縴λʱ���û�������ⲿ����������RAM�У��Ա�֤��ȫ�����С�C5402�ṩ����������Bootloader ������8λ��16λ����EPRO�ͷ�����8λ��16λ����I/O������8λ��16λ���пڷ����ʹ�����ͨ�ſڣ����˿ڣ�HPI������

�ϵ縴λ��C5402�����MP��MC���ţ����MP��MC����0�������Bootloader������Bootloader������INT2�����жϣ������HPI������ʽ�����������˿ڵ�ַΪ0FFFFH��I/O�˵�������ʽѡ���֣�Boot Routine Selection,BRS������BRS��XXXX00ʱ������I/O���п�������ʽ��BRS��XXXX1000ʱ������8λI/O������ʽ��BRS ��XXXX1100ʱ������16λI/O������ʽ����������봮�п�������ʽ����BRS��XXXX01ʱ������8λEPROM������ʽ��BRS��XXXX10ʱ������16λEPROM������ʽ��

�� C5402Ƭ��ROM�ṹ������I/O����װ�س������

C5402 �ṩ��4K��16bit ����ģROM����������ݼ���1��C5402�ϵ縴λ�����MP��MC����0�����F800h��ַ��ʼ����Bootloader�����ڽ���8λ���� I/O����������ǰ��C5402���ⲿI/OҪ����һϵ�е�ͨ�����磬������ͼ��ͼ1��ʾ��

������8λ����I/O��������Ƭ���£�

�к� Դ���� ע ��

(���) ..

END �������û��������

����תִ���û�����

�� CALL ��(21)�� �����ö������ӳ���

�� STL B,61h ���µ����ݡ������ȵ�Ԫ

�� CALL �� (21) �����ö������ӳ���

�� STL B,61h ���µ����ݡ������ȵ�Ԫ

�� CALL ��(21)�� �����ö������ӳ���

�� BC (END), BEQ ��B��0ʱ����

�� SUB ��01h,0,B,B ��B��1��B

�� STLM B,BRC��B��BRC

�� CALL ��(21)�� �����ö������ӳ���

���� STL B, 68h ��B�����ݡ�68H��Ԫ

���� CALL ��(21)�� �����ö������ӳ���

���� ADD 68h,16,B,B ��68H����B��B

���� LD B,0,A ��B��A

���� RPTD (20)��1; ѭ��15��19

���� CALL ��(21)�� �����ö������ӳ���

���� SSBX XF ��XF��1

���� BC �� (17),BIO��BIO��0��ȴ�

���� WRITA B ����B�������*A

���� ADD ��01h,0,A,A ������������

���� B �� (5)�� ����ת�����Ϊ5

���� SSBX XF ��XF��1

���� BC ��(22),BIO ��BIO��0��ȴ�

���� RXBX XF ��XF��0

���� BC ��(24),NBIO ��BIO��1��ȴ�

���� POETR 0000h,B ����0��ַ�˿ڡ�B

���� SFTL B,8,B ��B����8�B

���� SSBX XF ��XF��1

���� BC ��(28),BIO ��BIO��0��ȴ�

���� RXBX XF ��XF��0

���� BC ��(30),NBIO ��BIO��1��ȴ�

���� PORTR 0000h,68h ����0��ַ�˿ڡ�68

���� ANDM 000ffh,68h ������

���� OR 68h,B ��������B

���� RET ������

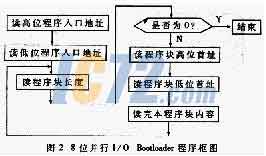

�����������У�END��Ÿ���I/O���������������ת�Ƶ���ڵ�ַ��֮��ת��61H��62H��������ڵ�ִַ���û�����1��4�ж�����ڵ�ַ���� 5��8�ж������ݿ鳤�ȣ���9��13�ж������ݿ���ַ����14��20�ж������ݿ顣Ϊ�˸��õ��˽���γ���Ĺ������̼���ԭ����ͼ2������8λ���� I/O Bootloader��������ͼ����21��34��Ϊ�������ӳ����ڸó����У�������XF��BIO�ź����ⲿI/O�����������磬���ź�ʱ����ͼ3��ʾ��

�� C5402����I/O����װ�ط�����ʵ��

������ Ӳ����·����

Ϊ������C5402 DSP 8λ����I/O Bootloader���������ʱ��Ҫ��������8031��Ƭ��������I/O������ͼ4ΪC5402��8031�����ӵ�·ͼ����ͼ�У�U3ΪTMS320VC5402DSP��U��Ϊ8031��Ƭ����U1��U2��ΪSN74AHC245����Ƭ��ϵͳ�е�EPROM

��·û�и�����

U1�� U2��DIR���Žӵأ����ݴ��䷽��ΪB��A��U2��B7��B4��B2��B0�ӵأ�B3��DVDD(3.3V)����CE�˽�ϵͳ��λ�źţ���֤�����ϵ縴λ�ڼ�U2��C5402�ṩ00001000B���ݣ�ʹ�����8λ����I/O����ģʽ��������λ�ź���Ч��U2�ģ�CE����1��Ƭѡ�ź���Ч������ϵͳ��U1�����������ݻ��������ƽת������U1��VCCD�˽�4.3V���������ǽ�8031�����TTL��ƽת����5402�ܽ��ܵ�CMOS��ƽ��U1�ģ�CE�Ͻ�8031��P3.3(��INT)�ţ���ϵͳ��λֱ��ִ��CLR P3.3֮ǰ�����ָߵ�ƽ���ڴ��ڼ�U1��Ч����֤��U2��������5402��������ݡ�8031��P3.0( RXD)��P3.1(TXD)��Ϊ�����źţ��ֱ���C5402�ģ�BIO��XF������JP3��JP4�ɹ��û�����ѡ��C5402��ϵͳʱ���Լ�ѡ�� C5402������ģʽ��

������ �������

�������Ϸ������������������8031����������ʹU1�ģ�CE��Ч��Ȼ��ȴ�C5402��XFΪ�͵�ƽ��XF����0����ʹ8031��P3.1�� ��0����BIO����0��C5402����ȴ�����״̬���������͵���������֮��ʹBIO����1��֪ͨC5402��ȡI/O�˿����ݡ������У�UC����Ĵ���ǰ��22���ֽ�����C5402�������룬�ӵ�23���ֽڿ�ʼ�����û�������롣

CLR P3.3 ��ʹU1(AHC245)��CE��0

W1: JB P3.0,W1 ��XF��1�ȴ�

CLR P3.1 ��ʹBIO��0

MOV R4,��00H ����ʼ����ַ�Ĵ���

W2: JNB P3.0,W2 ��XF��0�ȴ�

MOV DPTE,��UC ��ָ���û�������ַ

MOV A,R4 ����ַ��A

MOVC A,��A��DPTR ��ȡ�û�����

MOV P1,A ���͵���������

SETB P3.1 ��ʹBIO��1

W3: JB P3.0,W3 ��XF��1�ȴ�

CLR P3.1 ��ʹBIO��0

INC R4 ��ָ����һ����

CJNE R4,��0FFH,W2 �������

UC:�� DB 08H,0AAH,00H,00H

DB 00H,00H,00H,00H

DB 00H,08H,00H,25H

DB 00H,00H,00H,80H

DB 0F4H,95H,0E9H,27H

DB 0F3H,10H ������Ϊ��C5402�������� ���û��������

TMS320VC5402 DSP��C54�ؼ�������TI��DSP��������³�Ա�������伫�ߵ��Լ۱ȱ�Խ��Խ����û������ܡ������������ۡ�ͨ�õ�8031��Ƭ��ʵ��C5402 8λ����I/O Bootloader���ܣ�һ���棬���Ժܺõؽ������DSP������I/O��EPROM��֮������ݴ������⣻��һ���棬C5402 Bootloader�ɹ���8031������Ϊ��Э��������ʹ�ã��Ӷ����������ϵͳ������Ժ�ʵ���ԡ����й�����Ӧ��ǰ����

|