MAX+PLUSII��ALTERA��˾Ϊ�Լ���ϵ��EPLD��FPGA�ṩ�Ĺ���ǿ�����Ƽ������������ڸ������У��ṩ�˴Ӷ��ַ������롢����һֱ�������һϵ�������ܣ�������Щ���Ǻܸ��ӵ�ʱ���������˵��������һ�������ڷ����������е���Ƽ����湤������������Щ���ӵ�������Ե����������ˡ�

��һ�����ӣ���һ������FPGA��Ƶ��״��źŴ����������ǹ������ڸ������ָ��ʺ��龯�ʵ�ǰ���µ���С�ɼ������ȣ�������ijһ�����������������Pd��Pf�Ƿ�������Ҫ����Ȼ�����֮ǰ�϶��Ѿ�������������Է��������ܷ�����һϵ�еĹ�����������������ʵ�ֱ��뿼�ǵ�һЩ���⣬���ֳ�ЧӦ���㷨�ȣ��п���ʹ����ʵ�ֵ����ܱ�֮���۷��������½�������½������ж�����⣬���õ��źŴ����㷨������Щû�з��ֵ�ȱ�ݣ����������˵���ܹ���ȫ������������ͨ�������������Щ����Զ���ڲ������Ӳ�������з����ص��ԡ���������Ч�ʣ����и���ĵ��ԣ��������С�

Ȼ������������ͨ��MAX+POUSII�����Դ��ķ��湤�߶Ը�����Ƶ�������һ������ʱ���ͻ������������ѡ�һ����˵����IJ�����ͼ����ʾ�����У��ֹ����÷�������ڵ�ֵֻ�����������źűȽϼ�����������ڸ��ӵ������źž�����Ϊ���ˡ��������״��źŴ������������źţ�Ӧ������������ڵ��״�ͬ���źš��״�ز��źż���ȡ���ڽ����ŵ��Ĵ����������ɵģ�������Ӧ�и���������ȹ�ϵ�������������źŲ������뾭�ϸ����õ������������������ֹ����롣

���⣬һ�����ǶԷ������ķ���Ҳ������ֱ�ӹ۲죬ֻ�ܶ���ԽϼĽ�������жϡ����״��źŴ���������������ؿ���ʵ�飨����ʵ�飩��ͳ�������ܣ���ͳ�Ƹ���������µ�Pd��Pf������Դ���������и��ַ�������ʱƵ���������жϴ������Ƿ���ѵȡ��������Է������ķ���Ҳ���ܼ��жϣ����뾭ר�ŵ���ѧ������ܸ������ۡ�

�ɴ˿�����MAX+PLUSII�ķ��湦���Ѿ���������Ը�����ƽ��з����Ҫ�����DZ������ҷ�������Ȼ���������ãϣӣӣ��������������Ļ����Ͳ��������������ˡ������ڴ�����������˵������һ������л���Ӵ�����Щ����վ�ϵĴ������������ռ�������MAX+PLUSII��MATLAB������ͨ�ù���������

����֪����MATLAB��MathWorks��˾�Ƴ���һ�������ѧ�빤�̼���ĸ������ԣ�������������ѧ���㡢�Զ����ơ��źŴ����������硢ͼ��������һ�壬���м��ߵı��Ч�ʡ������Լ�����ز��������źţ����и��ֱ任��ͳ�ƣ��������Ļ�ͼ����Ҳ��Ϊǿ��������Щ�ص����ÿ����ֲ�MAX+PLUSII�ڷ��湦���ϵ�ȱ�ݡ���ˣ��������������һ������MATLAB���������ӵķ��������źţ����Է�������źŽ��з����ķ�����

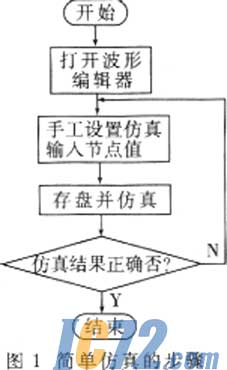

�����Ϸ��淽������

���������Ϸ�������

�����Ƚ���MATLAB��MAX+PLUSII���Ϸ�������̣���ʹ���������һ�����Ȼ���ٷֱ���ܸ����ֵ�ʵ�֡����Ϸ�������Ϊ��

����������MATLAB�в���ԭʼ�źţ���ת��Ϊ2/16�������У�

�����������Լ���д��MATLAB������һ����ʽ���������ļ���*.vec�����ı��ļ�����

��������MAX+PLUSII�У�����Ҫ�����FPGAԴ�ļ�������Ϊ����ǰ���̡��������룻

��������simulator��ѡ��File\Inputs/Outputs����������MATLAB�����ɵ������ļ�����������ȷ������ť����*.scf�ļ���

���������з��棻

������ѡ�˵���File\CreateTableFiles����������Ӧ��*.tbl�ļ������ı��ļ�����

�������ص�MATLAB�£������Լ���д�ĺ������Զ���Table�ļ���ȡ��Ҫ��������ݡ�����ת������Ϊʮ���ƣ������ɷ��������У�

�������Խ�����н��н�һ��������������

��.2���������ļ�

��MAX+PLUSII�ķ��������ļ�����һ���ı���ʽ�������ļ���VectorFile���������Ϊ��*.vec�������ļ�����һ����ʽ���ı������������źŵġ����ǿ��Ժܷ����ʹ���κδ��ı��༭������д�ļ����������ʱ�䳤�ȣ�����ԣ�����ʱ�䵥λ�����������ظ��������źţ���ʱ�ӣ����������������źš��������һ�����ļ��ļ����ӣ�

��ʱ�䵥λȱʡΪ�ԣ�

START0����������濪ʼ������ʱ�䣥

STOP1000��

iNTERVAL100��������ʱ�䲽����100ns��

INPUTSCLOCK��

PATTERN

01�����������ֵ���壺CLOCK��

��ÿ100ns��תһ�Σ�

INPUTSDATAINXDATAINY��

PATTERN���������������źţ�

%DATAINX��DATAINY%

0>00

220��10

320��11%����ʱ��������

570��01%���ں�ǰΪ����ʱ��ֵ��

720��11%���ںź�Ϊ��������ֵ��

��

INPUTSCLEAR��

PATTERN

0��1%��������100ns�������źţ�

100��0%100ns��CLEAR�źű��ָߵ�ƽ��

����������У�������һ������Ϊ200ns��ʱ���źš�һ��100ns��ǰ�����õ������źţ��ߵ�ƽ��Ч���Լ����������ź�DATAINX��DATAINY����ʵ��ʹ��ʱ�����ǿ�����ͬ���ķ�������ز���ʱ�ӡ���λ�ȳ����źš������ڸ��ӵ������źţ���������MATLAB��������Ȼ�������ʱ��ķ�ʽд�������ļ���

�ڲ������������ź�֮ǰ������ע�����¼��㣺

��һ��MATLAB�������Ǹ���������źţ�������ģ�������ΪNλ������������֮����һ������ת�������⡣��ˣ�������Ҫ����Ҫ���õ�A/Dλ����ԭʼ�źŽ���������

�ڶ�����MAX+PLUSII�ķ������У����ݿ��Բ���2/8/10/16������ʾ��ʽ������ʮ������ʾ�õ����������ķ�ʽ���ڱ�ʾ��Щ������ʽ��2/8/16������ʱ�ᷢ��������˱���������ź�ת��Ϊ2/16��������

����������ת����������Լ����ơ���ΪMATLAB�����ַ�������ʾ2/8/16�������ģ���Ȼ��һЩ���Ʊ任�ĺ�������HEX2DEC��DEC2HEX�ȣ������в���������Ҫ�������ڴ˻������Լ������µĺ�����

��.3��������ļ�

�����ļ������Ϳ��Խ��з����ˣ�������ת����Table�ļ������Table�ļ�ʾ�����¡�

INPUTSclkresetdin;

OUTPUTSy

UNITns��������ʱ�䵥λ��

RADIXHEX����������ʾ���ƣ�

PATIERN

��r��

��e

��csd��

��lei��

��ktny��

0.0��X00000=0000

40.0��X10000=0000

50.0��010000=0000

����

1475.0��110000=0000

1500.0��XXXXXX=XXXX

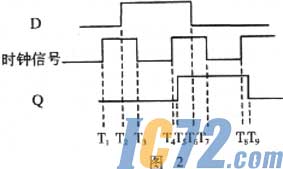

Table�ļ��Ĺ����������ļ�������ͬ�����Ŀ�ʼ������ע�ͣ�ͬ�����ԣ�������ע�����֣��������Ƕ����룯����źš�ʱ�䵥λ����ʾ���ý��ƵĶ��壬�������־��Ƕ����룯����ź��ڷ������б������У�����������ǰ����ʱ��ֵ���������ź����������ǹ��ĵķ����������ˡ�����Table�ļ�����Щ�ص㣬���ǿ��Ա���MATLAB���������ĵĶ�������ʱ��ֵ��ij����������ȡ�����γ��������У��Ա����������������Ҫע��һ�����⣬����Table�ļ��л��ÿһ���źŵı仯ʱ�̶����м�¼��������ͼ����һ����D�������IJ��ַ���ʱ������˵����ͼ��ʾ���ˣĴ������������ź�D��ʱ�ӣ��Լ�������ź�Q������һ�η����У�Table�ļ����¼��T1��T9��9���źű仯��ʱ�̣���ʹ������źŵ�ÿһ��ֵ����¼�˶�Ρ�������ǶԴ˲��������յ�ȫ�յĻ����ͻ�Դ˺�ķ������������鷳����ˣ�����ͬ������ϵͳ������ֻӦ��ȡ��Щ���ǹ��ĵ�ʱ�����أ�����ʱ�̵����ֵ��

��Ӧ��ʵ��

�������Լ�����ƹ�����ʹ�������Ͻ��ܵ����ַ���������Ƶ���һ���������״�ز��źŴ�����������ԭ�����źŵ��������ۺ��⣬���в����˽ϸ��ӵ��źŴ����㷨����ԭ����֤�β��õ��ǹ̶�����⡣����MAX+PLUSII�������źŴ���������ʵ���������Ҫ�ڸ���Pd��Pf�������£����ݾ�����㷨ȷ��������ޡ����ڽ��ջ��϶Խ��ջ�������ʾ�������в������洢�˴������ݣ�Ȼ�����������MATLAB���γ�һά���顣Ȼ�����Ͻ��ܵķ������������ݽ������ִ�����һ�Dz���ģ��ز��źţ��������ʵ�ز��źŲ������У����ź�������һ������Ȼ�ϡ�����ͬ��������γɶ�����ڵġ����źŻز�����������ȫ�������ġ����źŻز������ٽ��������Ҫ�������źţ���ʱ���źŵȣ����������ļ�����MAX+PLUSII�з���ֱ���ȡ�������еġ��У����źš��������������۽�����з���������ȷ��������ޣ����ɴ˽�����۷������������ܽ���������

��Ȼ��������ȫ�����������н������ܷ����ķ������������ܵģ���ֻ��ҲֻӦ���������ã����Dz�������Ŀ����Ϊ��ʹ���ǵ���Ʊ�ø����á���ʡʱ�����ɿ����Ͼ���һ�����������Ҫ�γ�Ӳ��������ʵ��Ӧ����ȥ������������Ʒ�ʵġ�

��֮������FPGA���������ص㣬ʹ������������������������Ӧ��Խ��Խ�㷺������Ϊһ������ߣ�����������������Ŀ����ԣ�����������������ֶ�����֤���ǵ���ƵĿɿ��ԣ������Ƶ�Ʒ�ʡ� |