����������ҵArteris��˾��ǰ������һ�ֿ�ȡ����ͳƬ������ϵͳ�����ͽ��������������Ӧ�������ิ�ӵ�Ƭϵͳ(SoC) ��������õĶ���첽ʱ�ӵ�Ƭ������ (NOC)ϵͳ��

NOC�������ΪƬ��ͨ���ṩ��һ��ȫ�µ������ֶΣ��ݳ������ܴ�ԼΪ��ͳ����ϵͳ��������SoC�����������ר��Ƭ�����ܹ�������Ƭ�����ߡ�����ARM��˾��AMBA�������������ܹ�����Sonic��˾�� SiliconBackplane����������

Arteris��˾Ӫ�����ܲ�Philippe Martin�ƣ�NOC�����������������������Ƭ��ͨ�š����������������Ӷ�̨������ķ��������Ƶ��ǣ�NOC�������������ֲ�ʽϵͳ������IP�鼰���ܼ��ȣ�����һ�𣬴Ӷ��ܼ��ټ�����������˶���������е���ʱ��Martin˵������ȥ���꣬���Ƕ�NOC�������൱����о���������ѧ�����о����������������ṩ���ò�Ʒ�����ò�Ʒ����Danube NOC IP�⡢���ڵó�NOC�ܹ���NOCexplorer���Լ���������SystemC�����ۺ�Verilog��VHDL��NocCompiler��

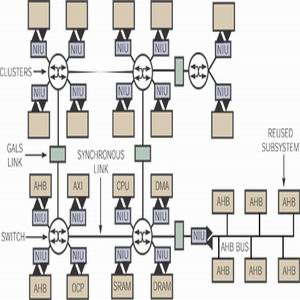

Martin��ʾ��NOC���������Ŀ����Բ����첽��Ʒ���������һ��оƬ�ϲ��ö��ʱ�Ӽ����ٸ�IP�飩����ơ����ڴˣ�Arteris��˾������ר�õ�Ƭ���Լ����ڷ����NTTP��NOC�����봫��Э�飩����������ӿڵ�Ԫ (NIU)�����ݰ����䵥Ԫ��������·��ɵ�Danube�⣬���������ִ������Э��ı�ҪԪ�ء�оƬ�ܹ�ʦ����NOCexplorer����������NOC���˽�ģ�����ó�һ��NOC�ܹ���NOCexplorer�û�����һ�ֳ�ΪGALS��ȫ���첽���ֲ�ͬ�����ķ�����ָ��һ��ͬ�������ù�������NIU��NOC�����Ƭ�ϲ�ڱ���������AMBA AHB�������������ߣ���AMBA AXI��������չ�ӿڣ���OCP������ʽ�ں�Э�飩2.0��ȵ��ں�������Danube���еĿ��ؿ����ż�Ⱥ���ͬ�����ӣ������е�GALS��������첽���ӡ�NOCexplorer����һ��������������������ϵͳ��Ϊ���н�ģ��

��оƬ�ܹ�ʦ�ó���������Ƶ����NOC���úͿ���NOCcompiler�����ɿ��ۺϵ�Verilog��VHDL��SystemC���Ա��ô�ͳIC������������ơ�NOCcompilerӵ�й����鹦�ܣ���ȷ������汾������һ���ԡ����⣬��������Ԥ�ۺϽι��Ƶ�·�����������������NOC��Ԫ�����ݱ�����һ�żĴ���ӳ�����NOC����Artisan����ֳɵ�EDA������90nm TSMC�蹤���ϴﵽ��750 MHz�Ĺ���Ƶ�ʡ�NOC������������Ϊ35����Ԫ�� |