1 概述

随着芯片制造工艺的不断发展及用户对数据实时性要求的不断提高。同时采样A/D转换器在实时性方面的巨大优势使其应用越来越广泛。MAXl320是Maxim公司最新推出的并行14位8通道同时采样器.其基本特征和参数如下:

●速度高,转换8通道的时间可达3.8μs,每通道的吞吐量达到250kps;

●模拟供电电压+4.75V一+5.25V。数字供电电压+2.7V~+5.25V,无需电平转换便可以直接与绝大多数的处理器直接相连;

●电压转换范围为+5V;

●16.6MHz的14位双向并行接口可与高速CPU直接相连;

●无需校准;

●双极性输入,无需负电源,提供+16.5V过压保护;

●先进,先出(FIFO)功能,减少接口开销,并可在转换结束或转换之间读取转换结果;

●典型模拟电流输入为.46mA.最大数字电流输入为1.6mA.典型输入阻抗8.66kΩ;

●动态特性:SFDR=90dBc.SINAD=76.5dB,直流精度为±2LSB INL,±ILSBDNL;

●7rmnx7mm,48引脚TQFP封装;

●可工作在扩展级温度范围(一40°~+85℃)。

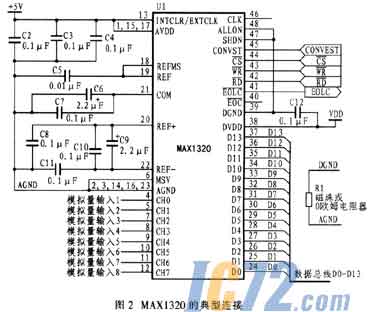

2 内部结构及引脚功能

MAXl320内部集成了带宽为IOMHz的S/H、+2.5V参考电压、内部时钟、8x14位SRAM以及选通采样通道的配置寄存器等。MAXl320内部结构如图1所示。

其中配置寄存器的设置如下:数据位DO―D7依次对应于模拟输人通道CHO―CH7.向其位写1选择相应通道,写O则关闭该通道。配置寄存器需同ALLON引脚一起决定通道是否选通。

引脚功能说明:

AVDD:模拟电源输入引脚。接+4.75V一+5.25V模拟电源;

AGND:模拟地;

CH0一CH7:模拟量输入通道CH0一CH7;

MSV:中值电压旁路;

INTCLK/EXTCLK:时钟模式选择输入。该引脚接AVm选择内部时钟,接AGND选择外部时钟输入;

REFMS:中值基准旁路或输入。应用时需将REFMS与REF连接。若采用内部基准.用一个不低于0.01μF。的电容将REFMS/REF节点旁路到AG-ND;若采用外部基准,用+2V一+3V的外部电压驱动REFMS/REF节点:

REF+:正基准旁路。应用时用一个0.1μF电容将REF+旁路到AGND,同时用一个2.2μF。电容和一个O.1μF电容将REF+旁路到:REF-;

REF一:负基准旁路;应用时用一个0.1μF电容将。REF-旁路至AGND。同时用一个2.2μF电路和一个0.1μF电容将REF一旁路到REF+;

DO―D13:14位并行数据总线;

DVDD:数字电源输入引脚;

DGND:数字地;

EOC:转换结束输出。低电平表明一次转换结束。在下一个CLK(上升沿或CONVST下降沿时变回高电平;

EOLC:最后转换结束输出。低电平表明最后一个通道的转换结束。当CONVST跳变到低电平为下一次转换时序做准备时,EOLC跳变到高电平;

CLK:外部时钟输入引脚;

SHDN:掉电输入引脚。该引脚为低电平选择正常模式,为高电平选择掉电模式。器件进入低功耗状态;

ALLON:通道使能输入。该引脚接高电平使能所有的输入通道(12H0一CH7),接低电平则只有被选中的通道才进行A/D转换;

CS:片选输入,低电平选通电路;

RD:读选通.将RD置为低电平将启动一次并行数据总线的读操作;

WR:写选通。将WR置为低电平将启动一次写操作,主要是对配置寄存器的操作;

CONVST:启动转换输入引脚。CONVST为高电平时将启动转换过程。模拟输入在CONVST的上升沿采样。

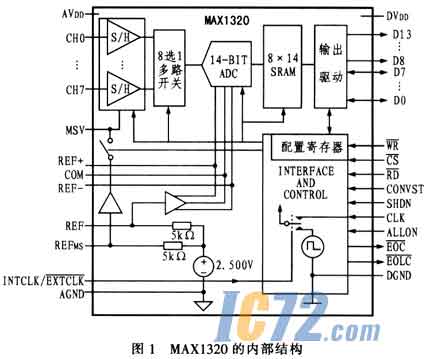

3 MAXl320典型连接

MAXl320的典型连接如图2所示.其中DVm引脚可接至+2.7V~+5.25V的数字电压。值得注意的事。为了提高A/D转换的精度。最好将数字地和模拟地分开走线.然后用零欧姆电阻或磁珠在一点相连。