ժ��Ҫ����������һ�����������IJ�����Ʊ��롣�����ڲ������� ����������������ԭ���Ļ����ϣ��������MAX+Plus��ƽ̨�ϻ���VHDL������� ��2��1��6���� �����������ķ���������ʵ���������˸ñ����������ȷ�Ժͺ����ԡ�

�ؼ��ʣ������룻���������VHDL��MAX+Plus��

1����

������Ϣ�������ŵ��д���ʱ�����ܵ��������ŵ�Ӱ�죬�������Dz��ɱ���ġ�Ϊ������֪����ȵ�����´ﵽһ����������ָ�꣬�ں�����ƻ����źţ�ѡ����ơ������ʽ��������Ƶ������ʱ������ʩ�Ļ����ϣ���Ӧ���ò�����Ʊ�����ŵ����뼼����ʹ�����ʽ�һ�����͡�������ͷ������Dz�����Ʊ����2����Ҫ��ʽ���ڱ��������Ӷ���ͬ������£���������������ڷ����룬��˾����뼸����Ӧ������������ͨ�ŵı�֮�У���GSM ��IS95��CDMA2000�ı��С�

Ŀǰ,VHDL�����ѳ�ΪEDA������ѡ��Ӳ���������,Խ��Խ�������ϵͳ���ʹ�� VHDL��������ɡ�ԭ����ͨ��VHDL������Ӳ��ϵͳ�����ˡ����ڴ浵,����ģ�����ֲ��AS C���Դ����Ľ�����Ϊ���㡣���,����IP�˵�Ӧ�õȷ��浣���Ų��ɻ�ȱ�Ľ�ɫ����ij��Ƶͨ��ϵͳ�У�����ʹ��VHDL��������ˣ�2��1��6��������������������������FPGAоƬ�ϵ���֤ʵ�顣

2����������

������ͨ������(n0,k0,m)�������Ч��Ϊk0/n0��m��ΪԼ�����ȡ�(n0 ,k0,m)���������k0�����롢n0�����������洢Ϊm����������״̬��λ�Ĵ�����ģ2�ӷ���������·��ʵ�֣�������ı��뷽����3�����㷽ʽ����ɢ�����������ɾ�������ʽ�˻��������⣬������ı�����̻�������״̬ͼ������ͼ������ͼ��������������Ƶı��������ǵ�Ӳ����·��ʵ�֣�ѡ���˶���ʽ�˻����� ��ϵͳ��ѡ������������ͼ1��ʾ���þ���������Ϊ��2��1��6��������������������

3������������

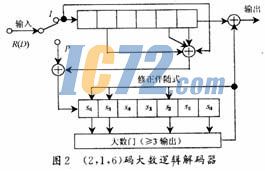

������Ľ���ɷ�Ϊ������������ʽ���2�ࡣ�������������Ǵ�����������Ҫ�Ľ��뷽�������ȿ����ھ�����������ֿ����ھ���ͻ������Ҫ������������������������롣 ������ѡ��2��1��6��ϵͳ������������Ĵ�������������ͼ2��ʾ��

ͼ2�У��ɶ�������Ϣ��Ԫ���ж�����У����Ԫ���������ѽ��յ���R(D)�е�ÿһ����ϢԪ�����������������ؼ���Ԫ����������յ��ļ���Ԫģ2�ӡ�������һ�£�������İ���ʽ����siΪ0������Ϊ1���Ѽӵõ�ֵ�������ʽ�Ĵ����мĴ档��������7����κ�ʼ�Ե� 0��ξ���������ʱ�������ŵ����Ϊ1����˵����0�� �ε���ϢԪ�д�����ʱ���õ�0�������ϢԪ����������������ˣ��Ӷ��������ǡ�ͬʱ�������ź�Ҳ����������ʽ �Ĵ�����������ʽ������ȥ�˴������ʽ��Ӱ�졣��������о���û���������˵����0�������ϢԪû�д�����ʱ�ӱ�������ֱ�Ӱ���ϢԪ��� ��

4��������������VHDL���

4.1VHDL��Ƶ��ŵ�����Ʒ���

�봫ͳ���Ե����ϵ���Ʒ�����ͬ��VHDL����Ǵ�ϵͳ������Ҫ������������Զ����£� toptodown������Ʒ����������ṹ�ص��ǽ�һ��� ��ƣ�������ʵ�壩���ֳ��ⲿ�����˿ڣ����ڲ��������ܡ��㷨�����ڶ�һ�����ʵ�嶨�����ⲿ�˿ں�һ���ڲ�������ɣ���������ƾͿ���ֱ�ӵ������ʵ�塣

���������VHDL���ƽ̨��Altera��MAX+Plus�� EDA������MAX+Plus������Ѻã�ʹ�ñ�ݣ���֧��VHDL��ԭ��ͼ��V�����ı��ļ����Լ�������EDIF�ȸ�ʽ���ļ���Ϊ������룻��֧����Щ�ļ�����������ƣ������ż������������Խ��й��ܷ����ʱ����棬�ܹ�������ȷ�ط�������֧�ֳ�APEX20K��APX��Mercury��Excalibur��Stratixϵ��֮�������Altera FPGA/CPLD���ģ������������в��õ�FPGA������Altera��FLEXϵ��оƬFLEX 10K20����MAX+Plus����������VHDL��ƵĹ����ǣ�

(1)��Text Editor��дVHDL����

(2)��Compiler����VHDL����

(3)��Waveform Editor��Simulater������֤VHDL����

(4)��Timing Analyzer����оƬ��ʱ�������

(5)��Floorplan Editor����оƬ�ܽ�λ�á�

(6)��Programer���س�����оƬFLEX10K20��

��ʵ�ʵĿ��������У����ϸ������跴�����У�ֱ�����ȶ���VHDL���ͨ�����еIJ���Ϊֹ ��

4.2����������VHDL���㽨ģ��top level����ϵͳ ���ܷ���

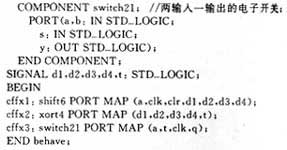

4.2.1����������������ģ�鼰���㽨ģ�˿ڵ�VHDL����

LIBRARY IEEE��

��MAX+Plus���������ɵı�����ͼ�η�����ͼ3��ʾ��

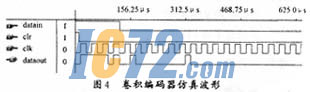

4.2.2����������VHDL���㽨ģ��VHDL���沨��

��

����������VHDL���沨����ͼ4��ʾ������ǰ����������Ϣ����datain=��1111��������Ϊ32 kP/s����Ӧʱ��Ϊ31. 25��s�������������������������dataout =��1111101 0010000000001������Ӧ����Ϊ64 kP/s�������۷������һ�¡�

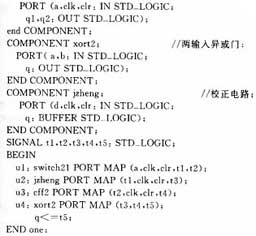

4.3����������VHDL���㽨ģ��VHDL�˿�����

4.3.1����������������ģ�鼰���㽨ģ�˿ڵ�VHDL����

LIBRARY IEEE��

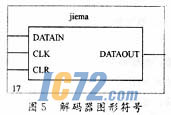

��MAX+Plus���������ɵĽ�����ͼ�η�����ͼ5��ʾ��

4.3.2����������VHDL���㽨ģ��VHDL���沨��

����������VHDL���沨����ͼ6��ʾ�����д�������Ԫdatain=��11111010010000000001�� ������Ϊ64kP/s����Ӧʱ��Ϊ15.625��s��������������������Ԫ���dataout =��111 1������Ӧ����Ϊ32kP/s��ʵ�ʷ��滹��֤�˵���������������Ĵ�������Ԫ���д���ʱ�ľ�������������۷������һ�¡�

5����

��ͨ�������VHDL�������ص�FPGAоƬFLEX10K20�ϣ�����ʵ����Ƶϵͳ�����ڲ������ ��ȡ���˽�Ϊ�����Ч���� |