大多数设计人员都使用运算放大器和 1% 公差的分立电阻器制作电平移位器。分立电阻器失配会将运算放大器的 CMRR(共模抑制比)限制在 40 dB以下,所以你就不能在要求CMRR很高的电路中使用运算放大器。差分放大器包含精密匹配的内部电阻,所以诸如INA133 等IC均能很容易地达到大约 90 dB的CMRR。只要微调内部的匹配电阻,它们均具有这样高的 CMRR。

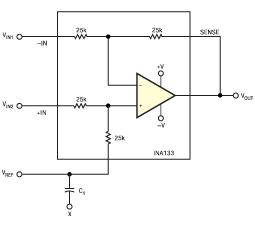

假定图 1所示电路的每个输入端都有相关噪声电压(VN1、VN2和VNREF)。放大器电路的传输函数是VOUT=(VREF+VNREF)+(VIN2+VN2)-(VIN1+VN1)。要注意基准电压使单一的输出信号或差分输出信号发生电平移位。一旦发生这种电平移位,你可能会将注意力转到消除噪声上来。只要精心布线,只要将信号差分耦合到差分放大器输入端,就能使信号输入端的噪声相等(VN1=VN2)。输入噪声是共模信号,因此差分放大器能最大限度地予以抑制(通常可抑制 90dB)。这时,VOUT=VIN2-VIN1+VREF+VNREF 。

图1,C1能使电平移位器起到一个低通滤波器作用,对基准噪声进行抑制。

现在,你必须消除基准噪声,以获得一个干净而又电平被移位的信号。你可以将 C1 的 X 端接地,将基准电压噪声旁流到地,但这种方法可能是无效的,因为基准信号源阻抗很低。然而,当你把 C1 的 X 端连接到信号源 VIN1 时,差分放大器就起低通滤波器的作用,从而抑制基准源噪声。

这一电路使差分放大器的输入阻抗很低(INA133 约为 25 kΩ),以利于阻抗匹配。因此,你必须保持信号源阻抗很低,以防止增益误差。为将增益误差降至最低程度,信号源阻抗应该低于输入阻抗的 1/1000。如果无法实现这钟情况,那么最好要对输入信号进行缓冲。

|