����

���ŵ��Ӽ����Ľ��������ֵ���Ҳ�õ���Ѹ�ͷ�չ��������Ƶ���ֱ����оƬ�����ĺ��IJ�������ADC����Ӱ�������ܵĹؼ�ģ�飬�����Ƹ����ܵ�ģ��ǰ��ADC��ΪIC��Ƶ���ս�����������һ����12λ���ȡ�80MHz�����ʵ�ADC�и���������ֵĺ��ĵ�·������絼�Ŵ��� (OTA)��

�˷Žṹ��ѡ��

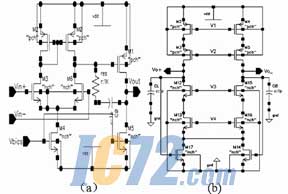

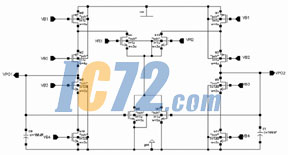

����ADC��Ҫ�����������˷ŵ�����ָ�꣬���1��ʾ���ݴ˿���ѡ���˷ŵĽṹ��Ŀǰ���������ֻ���������Ŵ����ṹ��ͼ1��ʾ��ͼ1(a)�Ǽ������˷ţ������д������ڷ�2(Vdd-2Vds,sat)����Ƶ�����Բһ����Miller��������ʹ����λԣ�ȱ�С�����ᵼ�µ�·�ȶ��Ա���һ�ָĽ��IJ�����ʽ�����ӵ������R2=1/Cc(1/gmb-R)�������ڹ��յIJ��ȶ��ԣ����Եõ���ȷ�ĵ���ֵ��ͼ1(b)����Ͳʽ�˷ţ�������·���Կ����ǵ�����ϵͳ�����貹�������Ƶ�����Ժã�����Ϊ��ֻ��2����֧·����˹��ĵͣ�������/����ڷ�С��ͼ1(c)���۵�ʽ��Դ��դ�ṹ�����Ľ�����Ͳʽ����/����ڷ�С��ȱ�㣬������4����֧·�����Ĵ����ȶ��Ա��������������Ľ��ͼ1(b)��(c)���ŵ㣬�����ȫ�����Ͳʽ������ǿ���˷ţ���ͼ2��ʾ�����������������������ĵ����Ҫ��

ͼ1 ���ֻ�������Ŵ���

��·ԭ������

���汶��

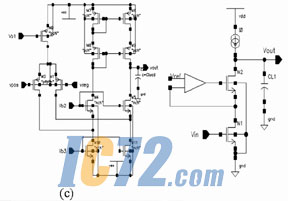

Ϊ��������棬�ڹ�Դ��դ�ṹ�ϸ��Ӹ�������Ŵ�������ͼ3��ʾ��������ǿ��Դ��դЧӦ�������˷ŵķŴ���ΪAadd��ͨ����С������������©���ķ��������������Aadd����Ҳ����Ч�ڣ�Rout��(gm2rds2(Aadd+1)+1)rds1+rds2�����У�gm2��M2�ܿ絼��rds1��rds2�ֱ�ΪM1��M2������迹����˵�·��ֱ������Ҳ������ͬ���ı�����Av=gm1Rout��-gm1rds1(gm2rds2 (Aadd+1)+1)��

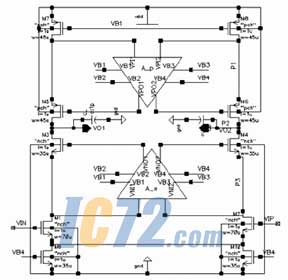

ͬ������ͼ2�е���Ͳʽ���˷ż��ϸ����˷ź���ֱ����������ΪAv=-gm1 [(gm5rds5rds7Aadd_p) //(gm3rds3 (rds9//rds1)Aadd_n)], ʽ��Aadd_n�� Aadd_p�ֱ��Ǹ����˷�A_n��A_p�ķŴ�����ͼ4��ʾ����n�����˷�A_p�Ľṹ��

p�����˷�A_n�����ƽ����˷ŵ�M3��M4�ܣ�n�����˷�A_p�����ƽ����˷ŵ�M5��M6�ܡ������˷Ų����۵�ʽ�ṹ������Ҫ̫����ٶȺͽ���ʱ�䣬�����β����ȡΪ���˷ŵ�1/10�������������·�Ĺ��ĺ������

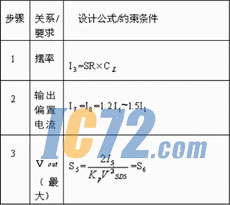

��2 �����˷ŵ���Ʒ���

Ƶ����Ӧ����

ͼ2��ȫ�����Ͳʽ��Դ��դ�˷ŵ���������P1�㣬Ƶ��Ϊwp1=-1/RoutCL���μ���λ��P2��P3�㡣ͨ������p�ܵ�Ǩ���ʱ�n�ܵ�Ǩ����С�����p�ܵĹ�������ѹ�ϴ��¿�����W/LҲ�ϴ�P2��ĵ��ݱ�P3�ĵ��ݴ���˿�����ΪP2��Ϊ�������㣬wp2=-gm5/Cp, ����gm5ΪM5�ܵĿ絼��Cp��Ҫ����M5�ܵ�դԴ����Cgs��M3�ܵ�դ©����Cgd�������˷ŵĵ�λ����Ƶ��Ϊwu=gm1/CL������gm1ΪM1�ܵĿ絼�������븨���˷�ʱ�����ӵ����沿����M5���γɱջ������������沿���ٶ�̫�죬��·�Ϳ��ܱ�ò��ȶ�������Ϊ�����˷�������һ���㼫��wdoublet�������Ʋ��ã��ͻ�����Ӱ���˷ŵĽ������ԡ����Ӧʹ����㼫�㾡�����������Ҿ���Զ�����˷ŵĵ�λ����Ƶ�ʣ�ͬʱ��ҪС�����˷ŵĴ������㣬����bWu�wdoublet�wp������b�DZջ�����ϵ����

ͼ2 ��Ͳʽ������ǿ�����˷�

���˷ź����˷ŵ���Ʒ���

�������Ͳʽ��Դ��դ���˷�ʱ�����ȸ����������ڷ���Ҫ�����������ѹVod�����þ�̬�����㡣��ͼ�ɵã�Vout,max=Vdd-(|Vod7|+|Vod5|), Vout,min=Vod9+Vod1+Vod3, ������ڷ�Ϊ1.5V, ��|Vod7|+|Vod5|+ Vod9+Vod1+Vod3=3.3-1.5=1.8V, ����p��M7��M5��Ǩ���ʵͣ������Ǿ�����0.45V�Ĺ�������ѹ��ʣ���ƽ�������M9��M1��M3��0.3V�����ɷ�ֵ��ѹ��ʽVgs=Vt+Vod֪����������С���빲ģ��ƽ����Vgs1+Vod9=1V��VB1����СֵΪVgs3+Vod1+Vod9=1.3V��Vod5�����ֵΪ��VDD-(|Vgs5|+|Vod7|)= 1.6V����ˣ��ۺϿ��Ǻ���������ƫ�õ�ѹVB4��VIN�� VG3��VG5�� VB1�ֱ�Ϊ��0.8V��1.2V��1.79V��1.6V��2.21V��

�ڽ��е�·���ʱ��������Ҫ�ֹ����������W/L������Ը���CMOS�ܱ��͵�����ʽIDS=Kn(W/L)(VGS-VTN)2(1+lVDS)�õ���ʽ�������絼����Kn=UnCox,l=������CoxΪ��λ�������������ݣ�NΪ�ĵײ���Ũ�ȣ�UnΪn���������ı���Ǩ���ʡ�ͬ���ɼ���P�ܲ�����

�۵�ʽ��Դ��դ�����˷ŵ���Ʒ������2��ʾ�������������Sn=(W/L)n��

ͼ4 n�����˷�A_p

������֤�ͽ���

��Cadence��Spectreƽ̨�£�����Ʋ���TSMC��˾��0.35mm CMOS����ģ�ͣ���3.3V��Դ��ѹ�£��ֱ���tt(����)��sf(��NMOS, ��PMOS)��ff(��NMOS,��PMOS)3�ֹ��������¶�����Ƶ��˷Ž����˷��档���������������IJ��õ�������ǿ����Ͳʽ��Դ��դ�ṹ��ȫ���CMOS����Ŵ�������110dB��ֱ���������棬320MHz�����������65�����λԣ�ȣ�ѹ���ʴ��?00V/ms, ����ʱ��С��6ns������С��5.7mW��

����

���Ķ������������ԭ����ȫ�����Ͳʽ��Դ��դ����Ŵ��������˷������ڴ˻����������һ��������������ȫ����۵�ʽ��Դ��դ����Ŵ�����������Ч��������棬ͬʱ������Ŵ������ٶȼ��ȶ��Ե�Ӱ���С����ˣ����˷Ŵﵽ��������ܵ�Ҫ���������ڸ��١��߾��ȵ�ADC�ȡ� |