TMS320F2812是德州仪器(TI)公司专门为工业应用而设计的新一代DSP处理器,它的性能大大优于当前广泛使用的TMS320LF240x系列。该芯片为32位定点DSP,最高主频150MHz,最小指令周期6.67ns,外部采用低频时钟,通过片内锁相环倍频;相对于TMS320LF2407只能寻址192KB地址空间,该芯片的外部接口最多可寻址4MB的空间;有3个独立的片选信号,并且读/写时序可编程,兼容不同速率的外设扩展;通过配置外部接口寄存器,在访问外部设备时不必额外增加延时等待,既提高了程序的实时性又减少了代码量。因此,灵活掌握和使用外部接口,对于DSP系统开发有很大帮助。本文结合实际系统,分析TMS320F2812外部接口的时序,设计了外部存储器扩展电路,根据所用的存储器芯片设置了接口时序,并提供了相关的电路原理图和外部接口时序配置的程序。

1TMS320F2812外部接口的特点

TMS320F2812外部接口(XINTF)采用异步非复用模式总线,与C240x外部接口类似,但也作了改进:

①TMS320LF240x系列,程序空间、数据空间和I/O空间都映射在相同的地址(0000~FFFF),最大可寻址192KB,对它们的访问是通过不同的指令来区分的,例如可用IN或OUT指令访问外部I/O空间;而在TMS320F2812中,外部接口被映射到5个独立的存储空间XZCS0、XZCS1、XZCS2、XZCS6、XZCS7,每个存储空间具有独立的地址,最多可寻址4MB。

②TMS320F2812中,有的存储空间共用1个片选信号,如Zone0和Zone1共用XZCS0AND1,Zone6和Zone7共用XZCS6AND7。各空间均可独立设置读、写信号的建立时间、激活时间及保持时间。

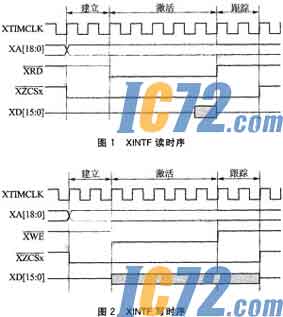

对任何外部空间读/写操作的时序都可以分成3部分:建立、激活和保持,时序如图1和图2所示。在建立(lead)阶段,访问存储空间的片选信号变为低电平并且地址被送到地址总线(XA)上。默认情况下该阶段的时间设置为最大,为6个XTIMCLK周期。在激活(active)阶段,对外部设备进行读写,相应的读写信号(XRD和XWD)变为低电平,同时数据被送到数据总线(XD)上。默认情况下读写该阶段的时间均设置为14个XTIMCLK周期。跟踪(trail)阶段是指读写信号变为高电平,但片选信号仍保持低电平的一段时间周期,默认情况下该阶段时间设置为6个XTIMCLK周期。因此,在编程时要根据外部设备的接口时序来设置XINTF的时序,从而正确地对外设读写。

2扩展存储器硬件设计

2.1外部存储器与TMS320F2812的接口电路设计

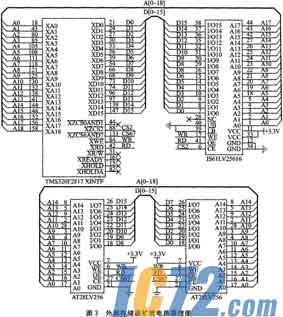

TMS320F2812内置18KBRAM。为了使用方便,本系统又扩展了256KBSARAM,芯片选用IS61LV25616(256K×16位),其数据访问时间为10ns。由于TMS320F2812采用统一寻址方式,因此扩展的SARAM既可以作程序存储器也可以作数据存储器。同时,为了保存掉电不丢失的数据,扩展了32KBEEPROM,选用AT28LV256,32K×8位,用2片组成32K×16位。外扩存储器与TMS320F2812的接口电路如图3所示,将SARAM分配在ZONE2,地址范围为0x80000~0xBFFFF,片选信号与TMS320F2812的XZCS2相连。EEPROM分配在ZONE6,地址范围为0x10000~0x107FFF,片选信号为XZCS6AND7。

2.2时序控制寄存器设置

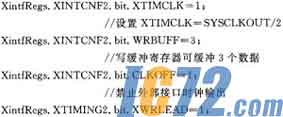

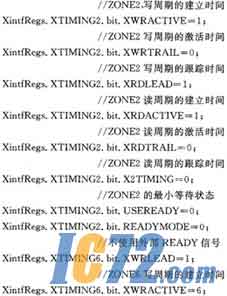

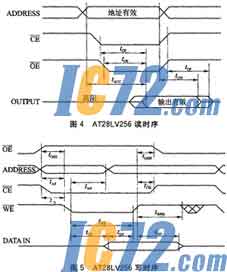

TMS320F2812的外部接口(XINTF)可根据系统设计的要求,分别配置每个空间的建立、激活和跟踪周期时间,以适应对不同速率外设接口的访问。配置过程中需要考虑外设器件的时序特性,必须使XINTF信号的时序与外设器件的时序一致才能正常工作。首先,必须设定XINTF模块的时钟,所有扩展外设的访问都是以XINTF时钟为参考的。本设计中,设定DSP内核频率(SYSCLK)为120MHz,设定XINTF频率为SYSCLK/2,即60MHz。根据器件手册,IS61LV25616的读/写周期为10ns,因此ZONE2配置为最小的等待时间,建立、激活和跟踪时间分别为16ns、16ns、0ns,写信号周期为16ns、16ns、0ns(对应寄存器设置为1,1,0)。AT28LV256的读写时序如图4、图5所示,读信号周期:建立时间为tCE与tOE之差,最大值为120ns;激活时间为tOE,最大值为80ns;跟踪时间为tOH,最大值为0,因此配置为33ns、50ns、0ns(对应寄存器设置为1,2,0)。写信号周期:建立时间为tCS,最小值为0;激活时间为tWP,最小值为200ns;跟踪时间为tCH,最小值为0ns。因此配置为33ns、217ns、33ns(对应寄存器设置为1,6,1)。外部接口寄存器设置的C语言程序如下:

结语

TMS320F2812的外部接口十分灵活、方便,通过独立的配置,能和各种快、慢速外设接口而不必在程序中额外添加延时等待。本文分析了TMS320F2812的外部接口及扩展外设时应注意的问题,以扩展RAM和EEPROM为例,给出了硬件电路设计并分析了接口时序;同时给出了接口时序设置的DSP程序,有助于工程人员更方便地进行基于TMS320F2812的开发和设计。 |