0引言

在高速源同步应用中,时钟数据恢复是基本的方法。最普遍的时钟恢复方法是利用数字时钟模块(DCM、)产生的多相位时钟对输入的数据进行过采样。但是由于DCM的固有抖动,在频率很高时,利用DCM作为一种数据恢复的方法并不一定合适。DCM的这种附加抖动会引起数据有效窗口的相应减小,这样就会限制高速电路的性能。常用的串行I/O技术需要时钟数据恢复(CDR)技术,而CDR技术需要模拟的PLL,其局限性是低噪声容限、高功率损耗及严格的PCB布局布线要求。基于对上述缺点的考虑,本文介绍了一种异步数据捕获技术,它不使用DCM就可以实现数据恢复,所以能获得更高的速度和性能。

1设计原理与实现方案

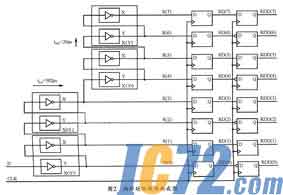

基于FPGA实现SoftSerdes主要由四部分构成:时钟产生单元、数据抽样延迟线、数据恢复状态机和输出弹性缓冲器。图1所示是SoftSerdes的实现原理图。SoftSerdes基本的实现过程是用一个双倍数据率(DDR)全局抽样时钟对多抽头延时线的延时数据进行抽样,它由数据恢复状态机利用边沿信息不断的从多抽头延时线中选择有效抽样,然后把正确的抽样送给输出弹性缓冲器。

1.1时钟产生单元

用一个320MHz的时钟可在双边沿抽样数据并驱动数据恢复状态机。对320MHz时钟进行5分频得到的64MHz时钟可作为串并转换和并串转换并的行数据的读写时钟。

1.2数据抽样延迟线

抽样延时线的构成如图2所示。对每个通道的输人数据均可利用8抽头的延迟线进行异步抽样。DDR操作时,每个通道有两路延迟线:一个用来在上升沿抽样;另一个用来在下降沿抽样。每条延迟线都由8个配置为反相器的查找表构成,这样既可保证上升和下降时间的对称,也能保证抽样数据之间的规则分布。但应注意:输入单元的输入节点必须以很小的skew到达两条延迟线。

基于两种基本的时序约束的时序分析决定了抽头延时和延时链的长度,抽样延时线的时序分析如图3所示。而时序约束分最好情况和最坏情况:最好情况的时序约束是整个延迟线的最小值必须大于数据总的抖动数,这个约束决定了抽头的个数;而最坏情况的时序约束是其最大的抽头延时值必须小于数据的有效窗口,这个约束决定了延迟线的构成。

最好和最坏情况的数学表达式分别为:

tJTT<tTPMIN[(n-2k)+1]

和tVAL>ktTAPMAX

其中,n是抽头数,k是数据有效窗口内数据最小抽样数,tTAPMIN和tTAPMAx是必需的最小和最大抽头延时,一般情况下,tJTT是总的jitter,tVAL是数据的有效窗口。

1.3数据恢复状态机

当抽头延时线对数据进行抽样时,数据状态恢复机就对这些抽样进行处理并最终输出有效位。边沿检测机制是通过分离穿过所有通道的各自检测结果获得的,每个通道再对上升沿抽头延迟线和下降沿抽头延迟线的8个抽样进行异或运算以得到每个通道各自的边沿检测抽样。在这个过程中,下降沿信号从180度相位的时钟域移到0相位的时钟域,接着边沿检测到的上升沿抽样和下降沿抽样与先前通道的边沿检测抽样值进行或操作,并把相或的结果送给下一个通道,从而将最后一个通道得到的最后结果送给状态恢复机。因为不管是上升沿抽样,每次还是下降沿抽样都只有一个数据跳变,所以在边沿检测抽样时至少有1bit被提取出来。边沿检测机制有四种行为:右移、左移、右跳和左跳。

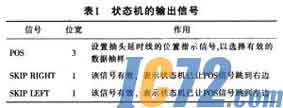

状态机总是保持至少一个抽样到数据有效窗口的边沿。在复位期间,状态机把抽头延时线的位置指示信号(POS)放到抽头延迟线的中央位置,POS信号用来选择有效数据抽样。其状态机的输出信号如表1所列。在正常运行时,抖动可能会引起数据有效窗口的漂移。状态机通过边沿检测机制不断的把边沿抽样值送到数据有效窗口,并决定POS指示信号和数据有效窗口边沿间的相对位置。如果POS指示信号离边沿太近,状态机则通过右移或左移POS信号对其进行调整,以使POS信号适当的离开边沿。接着,状态机会对POS指示信号更新并把更新情况反馈给抽头延时线。两个8∶1选择器可利用POS信号来选择上升沿抽样和下降沿抽样并将其作为有效数据输出。

状态机的工作原理如图4所示,其中0和1为抽样延时线对数据边沿的采样值。

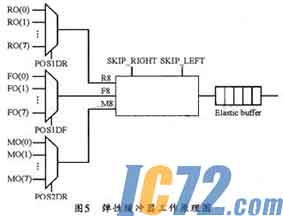

1.4输出弹性缓冲器

输出弹性缓冲器的作用是把1bit622Mb/s的数据串化为5bit/124.4MHz或8bit/77MHz的数据并输出,每个通道有5bit或8bit宽的缓冲器。因为622Mb/s的输人数据流会偏离输入参考时钟的相位达12UI左右,所以实质上它们是异步的。正因为这个原因,在311MHz时钟的每一个周期,其采样数据不一定是正常的2bits,而可能在时钟比数据慢时是3bits,时钟比数据快时为1bit。状态机产生的POS信号被放置在CLK311的时钟域,以让它控制3个8∶1的选择器来产生R8,F8和M8信号,其中R8是当前有效的上升沿抽样值,F8是当前有效的下降沿抽样值,M8是要求3bits位宽时的R8延时值。具体的跳变情况可通过状态机的输出信号右跳(SKIPRIGHT)和左跳(SKIPLEFT)来显示。而不管是SKIPRIGHT情况下的3bits抽样数据,还是正常情况下的2bits抽样数据,甚至是SKIPLEFT情况下的1bits抽样数据,它们都被放入5bits或8bits的移位寄存器。弹性缓冲器有5bit或8bit的位宽区域,在复位时,读和写信号指向缓冲器的中间,缓冲器的初始状态是半满的,可以容纳尽可能大的相位偏移量。弹性缓冲器的工作原理如图5所示。

2仿真

SoftSerdes的仿真环境如图6所示。发送方利用fifo造一些数据包,这些数据先经过低速并行数据接口,然后用8b/10b编码器对该并行数据进行编码。接着由SoftSerdes模块对该数据进行并串转换;而高速串行数据则通过光缆被接收方接收,再通过SoftSerdes模块对串行数据进行串并转换.然后用8b/10b解码器对该并行数据进行解码,最后得到低速的并行数据,这样,通过对该数据进行误码检测便可检测SoftSerdes在实现串/并转换过程中的误码率。

在图7所示的仿真波形中,发送方可将64Mbps的低速并行数据通过SoftSerdes并串转换为640Mbps的高速串行数据,而接收方则可将640Mbps的高速串行数据经SoftSerdes串并转换为64Mbps的低速并行数据。从仿真结果可以看出,SoftSerdes技术没有使用传统的CDR技术,而是通过320MHz的本地时钟来采样数据,从而实现数据的串并转换。

3结束语

由于SoftSerdes的整个设计都采用数字电路,所以具有比较高的噪声容限和比较低的功率损耗,也易于用FPGA对其进行实现,同时也可相对容易地完成产品升级。所以,该方法在通信、控制等需要用大规模FPGA进行设计的产品中有着广泛的应用前景。 |