1 ����

���ż��ɵ�·��ƺ��ռ����ķ�չ��Ƕ��ʽϵͳ��SOC���Ѿ���PDA�������С��ֻ�����Ϣ�ն��б��㷺Ӧ�á���������С�˵�·�ߴ磬���Ҿ��гɱ��������ɿ��Ըߣ����ĵ͵��ŵ㡣����˵Ƕ��ʽϵͳ��δ�����ɵ�·��չ�ķ�����ΪǶ��ʽϵͳ���ĵ�����������SOC���ɻ�ȱ�ġ����ࡱ��������������ֱ��Ӱ������SOC�����ܡ�

Ϊ�����CPU��Ч�ʺ�ָ��ִ�еIJ����ԣ��ִ��������Ѿ��㷺������ˮ����ƣ�����һЩ�ϸ����ܵ�CPU���Dz����˶��ij���ˮ�����ȣ����ԣ�CPU��ˮ�ߵ���ƣ�����Ϊ���������ܵĹؼ�����

2 ��������ϵ�ṹ

��������ƵĴ������ǻ���MIPSָ���64λRISC�ṹ��ִ��32λ������MIPSָ������弶��ˮ�ߡ����봦����Ԫ��32��ͨ�üĴ�����3������ܼĴ�����PC��HI��LO������PC�dz����������HI��LO����64λ�˳������㡣ϵͳЭ������CP0��32��CP0�Ĵ�����TLB�ṩ�ڴ��������ˮ���е��쳣�������ܡ����⣬���������ṩ��16k��ָ��Cache��8k����Cach e��

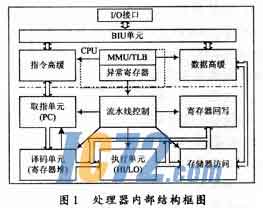

ͼ1��ʾΪ��������ϵͳ�ṹ��ͼ��ͼ������ر����˸���ģ���Ŀ��ƹ�ϵ��ʵ�߱�ʾ��������ˮ�߿����µ������������߱�ʾ������ˮ��ÿһ��֮���ɼ���Ĵ����ݴ��Ӧָ��Ŀ����źź����ݡ�

3 ��ˮ�߽ṹ

����ͼ1���Կ�������ָ��ִ��ͨ���ֳ���5����Ԫ��ͨ������ˮ�ߵ�ÿ����Ԫ֮��ʹ�ü���Ĵ����������Ӧ�Ŀ����źź����ݡ���Ӧ����ˮ�߽ṹ�ֱ�Ϊ��ȡָ��Ifet ch��������(Dec)��ִ�У�Exec�����洢��������Mem����д�ؼĴ���(WB)����ͼ2��ʾ��ָ������ˮ����˳��ִ�У�����ͬ����������ָ���ཻ�������Բ�����ˮ�߽ṹ��������ָ��IJ����ԣ�CPI���Ƶ���1��

4 ��ˮ�߿��Ƶ����

���ڲ������弶��ˮ����ƣ���Ҫһ�����ĵ���ˮ�߿���ģ��������ˮ���ϵĸ�����Ԫ���п��ƣ���ȷ����ˮ����ȷ��Ч�����С�ֵ��ע����ǣ�ָ������ˮ���ϵĴ��������Ǽ���ͼ2��ʾ��һ���������У����ǻ���ֺܶ������ƻ�ָ����ˮ��ƽ���ԣ���Щ�����У�

(1)������ˮ���ϵ�2��ִ�е�Ԫͬʱʹ��ͬһӲ����Դ������ð�ա�

(2)����ָ����1�����ڲ��������Ӧ��ˮ�εIJ�������˷�ָ����Exec����ALU������Ҫ������ڡ�

(3)ָ������Ľ����Exec���õ���WB����д�ؼĴ����ѣ�������ָ���ڽ��д��ǰ��Ҫʹ�ý����

(4)Branchָ���תָ���ERET��ָ�����ˮ���ϳ������ĸı䡣

(5)����ˮ�ߵ�ִ�й�������ʱ���������쳣������

��ˮ�߿��ƾ��ǽ���������⣬������ˮͨ���е�ָ��ִ�й��̣��ڸ���������ܹ���֤�����ָ�������������ִ�С�����Ҫ�������¸�����Ԫ��ͼ3��������ˮ�߿��Ʋ��ֵ�����ṹ��

4.1 �쳣������Ԫ

�쳣��ָ�����й����з����IJ���Ԥ����жϣ���ҪԤ�ȶ�����쳣��������������������ܷ�������ˮ�ߵ�Mem��Exec��Dec����Mem�����쳣���ȼ���ߣ���������ΪExec����D ec�����쳣��������ˮ���е����쳣��ָ���Լ�����ָ�Ҫ����ֹ���쳣�������������ˮ����ִ�С�

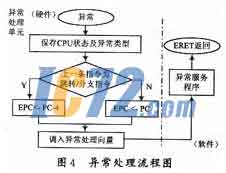

�쳣������Ԫ�ռ������쳣�źŲ�������е����ڼ�⣬ȷ���쳣�ļ�ʱ��Ӧ��������쳣ͬʱ������Ҫ�ж��쳣�����ȼ�������������������ȼ����쳣����ʱ�쳣������Ԫͨ��������Ԫʹ��ˮ����ͣ2�����ڣ����쳣��Ϣ����CP0�Ĵ���������EPC��������ˮ�߳�ˢ��Ԫ��ֹ��ˮ���ϵ���Чָ���ˮ�ߵ����쳣�������������¿�ʼִ��ָ���ͼ4��ʾΪ�쳣���������̣�Ӳ�������������쳣������Ԫ������ɣ���������Ϊ�쳣��������ִ�й��̡�

4.2 ��������ģ��

�����ķ�����Ҫ�����¼��������һ��������ˮ���е�2������ģ��ͬʱʹ��ͬһ��Դ����ð�գ���ʱ�ȴ���Դ����ˮ���Լ�ǰ�����ˮ����Ҫ�ȴ�������������ijһ��ˮ���IJ�����Ҫ���ʱ�����ڣ�������ˮ���ϵĸ�����ˮ���ȴ������ڲ�������ɡ�������������������ģ����ͣ��ˮ��ֱ���������������Ӳ�ͬ��ˮ��ͬʱ������ͣ��ˮ�ߵ�����ҲҪ�ж���ͣ��ˮ����������ȼ���

������Ԫ�ռ������źţ�����Ӧ������ȼ��Ļ����źš����жϻ������ͺ�����Ӧ��ִ�е�Ԫ����Stall����ˮ��ֹͣ���źţ����źű���Ϊ������ʱ�����ڡ�

4.3 ���ȼ��б�ģ��

�����ض����쳣����������Ӧ����ˮ�ߵ�ijһ��������ˮ��ָ���ִ�еĹ������쳣�ͻ���Ҳ��ͬʱ���������ȼ��б�ģ������쳣������Ԫ�ͻ���������Ԫ�������쳣�뻥���������ź����ж������쳣����ģ������ֹ��ˮ����ִ�е�ָ����ɻ�����Ԫ����ˮ����ͣ��

�쳣���ڽϸ����ȼ�ʱ�������쳣��ָ������ָ�Ҫ��ֹ����ˮ���ϵIJ���������δ�����Ļ�������������������ڽϸ����ȼ�ʱ���쳣�źű��֣�ֱ����ˮ�����ϸ����ȼ��Ļ����ź�ʱ��ˮ����Ӧ�쳣��

4.4 ��ˮ�߳�ˢ

����ˮ�����еĹ����У����ڳ���ִ�еIJ�ȷ���ԣ�������쳣��������ת���ӳ�����쳣�������ص����������˳��ִ�е�ָ����仯�����ǣ����ڲ�ȡ����ˮ����ƣ���ָ��˳�����仯ʱ��Ҫ�����Ѿ�������ˮ�ߵIJ���ָ�������ָ���ַ����װ��ָ�

��ˮ��Ϊ�˳�ˢ��Ӧ��ָ���ָ��棬Dec��Exec��Mem���Ŀ����źż����˶�·ѡ������ͨ����ˮ�߳�ˢ��Ԫ������ѡ���ź���ѡͨ�����źţ����������ѡͨ�����ź�����ɶԸ��������Ŀ��ƣ����Ҫ��ˢijһ����ˮ���ϵ�ָ���Exec����������Ӧ��flushExe c�ź�ѡ��0����ִ�пղ���������ˢ����ˮ�����Կ���ִ����һ��NOPָ�

4.5 ������·

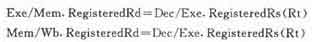

ͨ������ˮ�߽ṹ�ķ������֣�����һ��ִ�н��Ҫд�ؼĴ�����ָ���Exec�������������Ҫ��WB����д�ؼĴ����ѣ������ָ�������Ҫ�ý��������Ҫ�ȴ�ֱ������д�زż�����ˮ��ִ�С���ͼ2�еĵ�һ��subָ�$1��$3����Ľ�����浽$2�Ĵ����������C3���ڵõ���C5����д�ؼĴ�������������and��orָ��ֱ���C4��C5ʹ��$2��ֵ�ͻ��������Ľ������add��sw��C6��C7ʹ��$2�Ĵ�����ֵ�ͻ�õ�ϣ���Ľ����Ϊ�˱�ָ֤������ˮ������ȷ��Ч��ִ�У���������ˮ�߿�����������������·��������д�ؼĴ�����ǰ���ó��Ľ������ˮ������ݴ�Ĵ����е���Exec��ʹ�á��ж��Ƿ����·��ѡ�������Ϊ��

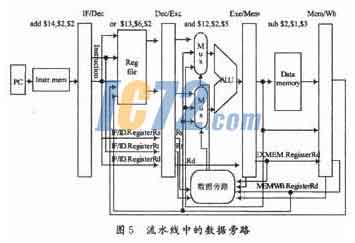

ͼ5��������������·�ṹ����ˮ��ͨ��ʾ��ͼ����ʾ��ͼ2��ָ������C4������ˮ�ߵ�״̬��

4.6 ����ð�ռ��

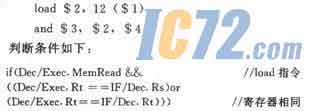

������·��������ˮ��ͨ��Stall���������ð�յ����⣬�����ָ���ִ��Ч�ʡ����ǵ�loadָ������һ��ָ����ͼ��ȡ�Ĵ�����loadָ��Ҫд�ļĴ�����ͬʱ��load��������Me m���Ӵ洢�����룬��Exec��ָ�����ҪStallһ�����ڲ���ͨ��������·��Mem/WB�Ĵ����õ����ݡ��磺

��loadָ�����Exec����andָ�����Dec������ʱ�жϵ�loadָ��װ�ص�Ŀ�ļĴ�����andָ���Դ�Ĵ�����ͬ���ͻ��������ð�գ���ʱHDU��Stall�ź�ʹandָ��ȴ�һ���ڣ�loa dָ����Mem���õ����ݺ�ͨ��������·���ƽ������ð�ա�

����ð�ռ�ⵥԪҲ����CP0�Ĵ�����ð�ս����˼�Ⲣ������ˮ�߲�ȡ��Ӧ�ı�����ơ�

5 ָ�����

��Ϊ��������ˮ�ߵĿ��ƣ���������ˮͨ�������и���ָ������������ˮ�ߵĿ����ź��ܷ����Щָ��������ˮ���ϵ�ִ�н��о�ȷ���ơ���������������������������FPGA��֤���ڷ���ƽ̨��FPGA��֤���������˸��ֿ��ܵ�ָ��������������ˮ�߿����źŵı仯��ȷ������������������Ŀ���ģ���ָ����ˮ�ߵ���ȷ���ƣ����ﵽ�˽ϸߵ�����Ч�ʡ�ͼ6�Dz����������ƽ̨�Է���itlb_miss exception�ķ��沨�Ρ�

�弶��ˮ�߿��Ƶ�Ԫ�������˴�������ִ��Ч�ʣ��ﵽ��64λ�������ĸ�������ƣ����������ٶȴﵽ��120 MHz���н�ǿ��DSP���ݴ������������ҿ�������WinCE��Linux��Ƕ��ʽ����ϵͳ��

|