有时候,用最新和最好的工艺技术设计一款 SoC(单片系统),并不是影响成本敏感的消费电子市场的方式。LSI Logic 工程师在设计 LSI 的 Zevio 1020 多媒体应用处理器平台时,就认真地关注着这个经验。

1994 年 12 月,教育电子公司 VTech 和 IP(知识产权)开发商 Koto 委托LSI Logic公司创建一个多处理器 SoC,以运行 VTech 的 VFlash “寓教娱乐系统”(图 1)。LSI Logic 过去是一家 ASIC 供应商,一直在向销售标准产品过渡。因此,当 VTech 委托 LSI创建SoC 时,LSI 的管理层决定抛弃传统的 ASIC 设计,而采用一种 通用多媒体处理器平台。

Zevio 项目架构师 Shinya Fujimoto 称,他的 LSI 设计团队必须在几项约束下工作:建立一个通常模块化的多处理器平台,这样 LSI 工程师可以通过块的交换,快速创建出派生产品;采用成熟的 0.13 微米低功耗工艺技术实现 SoC,使成本保持在合理的低位,并且仍能达到性能与功耗目标;最后,在九个月内完成初始SoC平台。

Fujimoto 说:“我们的背景是从事消费类ASIC。我们做过 PlayStation 和 PlayStation2 中的芯片,以及某些 iPod 设计,并且,在这些产品开发期间,我们注意到自己在重复调整芯片中非关键部分时花费了大量时间。这就是我们决定开发这一架构的原因。”

Fujimoto 称,定义 Zevio 架构的第一步是要符合 VTech 和 Koto 的系统架构。他说:“我们试图从客户那里获得尽量多的反馈乃至抱怨,以确定设计过程中的潜在瓶颈。”

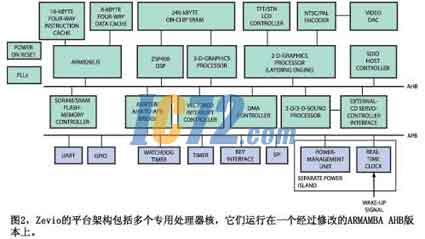

Fujimoto 称,Zevio 不是一个典型的应用处理器(图 2)。他表示:“我把它叫做一个异种多处理器。它有多个处理器,它们各不相同,但并行运行,每个处理器都专门完成一些自己擅长的任务。”

团队确定,SoC将包括一个用于一般处理的ARM9处理器。LSI小组将创建一个定制的图形处理器,以及音频控制器核与内存控制器核,而设计将包括一个LSI Logic的ZSP DSP核,用于完成更多的即时解码与编码型应用。据Fujimoto说:“对我们来说,关键是让多个处理器独立地运行。”这意味着,每一个处理器都是自己的主控者,无需CPU干预就可完成自己的运行。“我们必须确定它们都能高效地运行,不会造成总线或内存的瓶颈问题。”

采用成熟的低功耗 0.13 微米工艺(从一家未披露名称的台湾伙伴处获得)做设计实现,而不是采用 90 纳米或 65 纳米工艺,这有助于保持芯片的低成本,稳定电源管理,并且避免使用 DFM(可制造性设计)工具,所有这些都加快了设计进程。Fujimoto 称,该芯片面向成本低于 100 美元的系统应用。“任何人都可以造出一款巨大的芯片,但有些人正在努力挣扎,尤其是那些无名的视频游戏供应商,因为增加的芯片成本都要进入消费产品费用中。”

Fujimoto 指出,很多公司过快地跳到了最新最好的工艺,而他们本可以用更成熟和更稳定的工艺完成更多任务,例如用 0.13 微米工艺。“有些人不考虑 0.13 微米,认为它比较低端,但我们感觉可以通过智能工程化建立一个高端设计。客户会从竞争者那里听到很多有关高性能的故事,这个那个,全是一些浮夸的词藻。但到最后,还是要归结到花了钱就要获得最好结果。”他坚持认为,0.13 微米工艺的成熟、成本、性能构成了最佳选择。

LSI 希望 Zevio 成为一个可重用平台,而不只是一片 ASIC,于是一个关键的要素是建立一个独特的内核,可以将它与一系列 LSI 甚至第三处方供应商的内核结合起来。但是,架构规范的一个主要部分是新式图形处理器内核设计。LSI 与 IP 供应商 Koto 合作开发 Zevio 的 3D 图形处理内核。Fujimoto注意到,以前曾有多个 Koto 工程师在任天堂 GameBoy 设计团队中工作。Fujimoto 说 LSI 在这个领域中几乎没什么阅历,因此欢迎 Koto 的经验。“他们为软件开发人员需要的特性提供了大量经验,帮助我们将很多这类技术诀窍转化为硬件。”

Koto 的团队完成了大部分规范工作,并对内核做了验证,而 LSI 设计者则负责内核的设计和 RTL 实现。16位的3D图形内核只需要 30万个门,在 75 MHz 运行时功耗为20mW,每秒可以画 150 万个多边形。

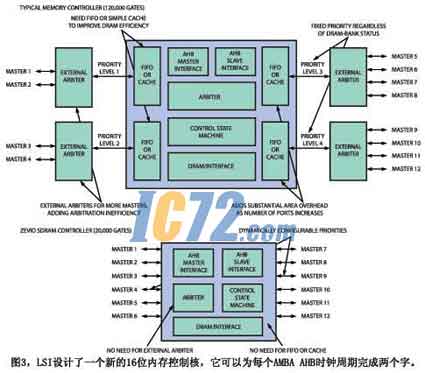

Fujimoto 指出,其它潜在的瓶颈是内存控制器及其与系统内存的接口。据芯片设计者讲,虽然他们很容易做出一个32位总线接口,使之快速运行并得到所需性能,但 LSI 必须考虑如何从一个16位接口内存获得相同的性能,以实现好的成本效益。

设计团队必须从头设计一个高效的控制器内核,它将采用一个16位 接口,并且考虑了效率仲裁(图3)。Fujimoto 称:“当查看一个16位接口时,我们关心的是获得一个很好的时序窗口,以便向SDRAM 发送很多指令。”Fujimoto指出,控制器可以在每个总线时钟周期取得两个字。“我们申请了该技术的专利。它使我们能够有效地用这些时序槽打开多个内存库。”Fujimoto认为这一进展是架构中的关键创新。

团队编写控制器的 RTL,然后运行概念验证仿真。他说:“我们看到了很多优于典型内存控制器设计的改进。在这个阶段,我们证明了可以在一个 16位接口上获得良好的性能。”

Fujimoto 称,接下来,团队要查看有关的总线协议瓶颈。他们决定 采用流行的 ARM AMBA(先进微控制器总线架构)AHD(AMBA 高速总线)协议,但必须寻找克服AHB中部分低效的方法。他说:“我们必须看到,它无法突发式写入随机地址,并且不能规定足够多的突发写入。”为了解决这些问题,团队自己编写了 AHB 扩展,使内存控制器的效率翻了一倍。

在解决了规范阶段的多数问题以后,设计团队(其时有10个~15个设计与验证工程师)开始作RTL设计。Fujimoto将他的团队划分为多个小组。他说:“一个小组专注于内存控制器,一个管图形内核,另一个做音频内核,其它小组负责整体集成。”

Fujimoto称LSI的传统方法是让每个小组作设计,然后验证各个单独的块,最后用仿真器将这些块与系统中的其它核作验证。但他的团队这回首次采用了一种FPGA原型化系统,对图形核、内存控制器和一个 LSI 开发的音频处理器作验证和软、硬件的确认。

Fujimoto说:“在一个仿真环境中验证这个设计可能会有太多的极限情况。这是我们第一次采用FPGA原型化系统。回想起来,我们应该在设计早期对各个内核多做一些验证。”Fujimoto回忆说,一旦FPGA系统工作起来,事情就会进展得很快:“当我们遇到问题时,我们可以在连接到 FPGA 原型板的 LCD 屏幕上看到它。我们可以简单地停下调试器,查看错误发生处的内部寄存器。”

小组还找到了一些后来证明是 FPGA 编程软件中的错误(而不是设计的)。Fujimoto 说:“我们并不知道正在对付的错误是否是工具供应商造成的。FPGA 供应商提供的 FIFO 控制器也有问题。”

Fujimoto 指出,图形小组在规范阶段创建了一个图形核的 C 模型。Fujimoto 说:“我们本可以用这个 C 模型作验证,但要做太多工作才能更新 C 模型和 RTL。”他指出,如果你采用一种固定的规范,则可以用 C 模型方法,此时可以用 C 模型输出来验证 RTL 的输出。但在 LSI 的案例中,当开始 RTL 时规格并未全部完成。他说:“一旦我们的 FPGA 系统开始运行了,我们就抛弃了 C 模型。”当设计在 FPGA 原型化系统上稳定下来时,小组还开始了驱动程序的初步开发。

原型电路板成为了验证电路板的基础,LSI 现在向希望用 Zevio SoC 开发其它系统的客户提供这块验证板。当小组的 RTL工作稳定下来后,便运行一个试验综合和一个试验布局,在初步布局的一部分中填充“空门”,以获得有关区域与核尺寸的一个粗略思路。Fujimoto 称他的团队由Synopsys 作综合,而由Magma 作布局和布线。

Fujimoto 称,实验布局对确定内存块的正确布放尤其重要。设计中带有 240 kB SDRAM。因此,Zevio 布局小组必须与 RTL 小组一起工作,将各个块分解,以保证多个核能够高效地访问内存,而不致占用太多的布局空间。他说:“我们有这么大的内存,但我们同时允许图形引擎和 DSP 访问相同的内存。在功能寄存器中,我们指定了哪个核有权访问内存,哪个将访问,这样我们就必须为 DSP 和图形引擎预先定义某些段。”为实现这个目标,布局与 RTL 小组通过多次重复,确定了内存的最佳布局。最后,整个 Zevio SoC 包含200万个门。

为保持设计低功耗,小组采用了一个多电压阈值的 0.13 微米库。Fujimoto说:“我们的想法是,将整体设计用所有低泄漏、低性能门作综合,然后确定时序中的瓶颈和关键路径,并将这些路径转换为高速门。”通过这个过程,团队就能够实现低泄漏与高性能晶体管的正确混合。

Fujimoto 称物理验证和设计出带都相当顺利。“原型硅片回来了,三天以后,我们所有的演示都在实际系统上运行起来。客户能够提前一周回家。采用成熟的技术,以及在过程的早期作验证和预备工作,所有这些都得到了真实的回报。”

电路板开发的快速“结束”也意味着 VTech 的软件小组可以快速地进入产品开发阶段,最终使 VTech 在 2006 年圣诞期间及时将系统推向市场。

但是,VFlash 并非 Zevio 系列产品的唯一应用。事实上,Fujimoto 称由于设计团队创建的 SoC 模块化,LSI 可以为其它客户的应用作修改。Fujimoto 说:“我们平台的设计目标是,只需六个月就能创建出派生的平台。”

他指出,模块化平台使用户能够相当容易地将 ARM 核换成 MIPS 核,因为 LSI 同时拥有两者的许可。用户还可以换用一些外设核。LSI 正在为系统增加 USB 支持。Fujimoto 称,下一代 Zevio 平台也将很快用 DDR 代替 SDRAM。虽然 Koto 为平台创建了最初的操作系统,但 LSI 正在扩展该平台支持的操作系统数量,现在可以工作在 Linux OS 和 Windows CE 上。

Fujimoto称,他的团队已在 Zevio 上为一个匿名客户完成了另一个项目。他说,硅片已经生产,但该客户还没有推出产品。

LSI 在 2004 年 12 月开始 Zevio 规范的制定过程,在 2005 年底启动设计,在 9 个月后的 2006 年 9 月进入生产。

Zevio 项目是消费市场中成功的又一个案例,说明成功并非总是意味着采用最新最好的工艺技术实现最快的 SoC。LSI 的团队在架构阶段作了大量规划,并在整个过程中做了一些创新的工程实践,建立了一个比较强大而有性价比的平台,帮助 VTech 抓住了市场窗口,LSI 也获得了一个帮助其它客户实现商机的通用工具。我们颇有兴趣的是 LSI 会在多长时间内将 Zevio 继续作为可行平台,以及能为其它客户创造出多少派生产品。 |